pcba如何选测试点

在PCBA(Printed Circuit Board Assembly,印刷电路板组件)设计和制造过程中,合理选择测试点是实现高效、可靠测试(如ICT、飞针测试、功能测试、边界扫描)的关键。以下是如何选择测试点的主要考虑因素和原则:

核心目标

- 可访问性: 测试设备(针床、飞针探针、示波器探头等)能稳定、可靠地与测试点进行物理接触。

- 覆盖性: 测试点需覆盖所有需要测试的关键信号、网络和元件引脚,以达到所需的测试覆盖率。

- 信号完整性: 测试点的引入不应显著恶化信号质量(尤其对高速信号)。

- 可制造性: 测试点本身的设计应易于制造,并在制造工艺中受到保护。

- 可维护性: 便于生产调试和后期维修诊断。

选择测试点的具体原则和考虑因素

1. 位置选择

* **避开元件:** 测试点必须远离高大元件(如电解电容、变压器、散热器)、插座、连接器等,确保测试探针或夹具能垂直无障碍接触到测试点表面。通常需要预留足够的**禁放区**。

* **均匀分布:** 测试点在板面上应尽量均匀分布,避免局部过于密集或稀疏,有利于平衡测试夹具的压力和探针寿命。

* **优先关键区域:** 时钟、复位、电源、使能信号、总线、关键控制信号、模拟信号输入/输出端、连接器引脚附近通常是重点区域。

* **板边优先:** 尽量将测试点放置在靠近板边的位置,方便手动测试探头接触(特别是功能测试、维修时)。

* **双面布局:** 如果板子双面都有元件,尽量在**底面**设置更多的测试点(底面通常元件较少、较矮)。若必须在元件面设置测试点,需确保该点上方无遮挡且元件高度允许探针接触。

* **远离机械接口:** 避免设置在连接器插拔区域、螺丝孔、板弯/板切应力区附近。2. 测试点类型选择

* **关键信号点:**

* **电源:** 所有主要电源电压输入点、关键芯片/模块的电源输入引脚附近(VCC、VDD、AVDD等)。每个独立的电源域都需要测试点。

* **地:** 提供足够数量的、低阻抗的接地测试点(GND)。它们至关重要,是所有测量的参考点。

* **时钟:** 主要时钟源输出、关键器件时钟输入点。

* **复位:** 系统复位信号线(通常需要上拉电阻测试点)。

* **关键控制信号:** 使能、片选、中断、读写控制等。

* **模拟信号:** ADC/DAC输入输出、传感器接口、运放输入输出、参考电压等。

* **数字总线:** 地址线、数据线、控制线(根据测试覆盖率要求选择关键线或全部)。

* **接口信号:** 重要通信接口(如UART TX/RX, I²C SDA/SCL, SPI MOSI/MISO/SCK/CS, USB D+/D-)的连接点。

* **元件引脚:**

* **关键元件:** 微处理器、FPGA、存储器、电源管理IC的所有引脚或其关键引脚(根据测试策略)。

* **分立元件:** 电阻、电容、电感、二极管、三极管、MOSFET等的两端(用于测试开短路、元件值)。对于电阻/电容网络,通常两端都需要测试点。

* **连接器引脚:** 无法通过针床直接接触的连接器引脚,需要在PCB走线上“引出”测试点靠近连接器。

* **特定测试点:**

* **JTAG/边界扫描:** TCK、TMS、TDI、TDO、TRST# (可选) 信号点。这是实施边界扫描的关键接入点。

* **功能测试点:** 专为功能测试预留的激励输入点和响应输出点。3. 物理规格

* **尺寸:** 直径通常建议在 **0.8mm - 1.5mm (32mil - 60mil)** 之间。太小不利于探针接触和定位;太大占用空间。常用尺寸为 **1.0mm (40mil)**。

* **形状:** 通常是圆形焊盘。方形或椭圆形也可,但圆形最常用且接触稳定性最佳。

* **间距:**

* 相邻测试点中心间距**至少**需要 **2.5mm (100mil)** 或更大(具体取决于测试夹具探针的最小间距要求)。密集区域需严格遵守夹具规范。

* 测试点边缘到元件本体边缘或SMD焊盘边缘的距离应**至少 1.0mm (40mil)**。

* **阻焊开窗:**

* 测试点表面**必须开窗**,露出金属(通常是裸铜、镀锡/铅或镀金),严禁被阻焊油覆盖!

* 开窗直径应**大于**测试点焊盘直径,确保探针能完全落在金属面上。通常大出 **0.1mm - 0.3mm (4mil - 12mil)**。

* **表面处理:** 选择不易氧化、接触电阻低、耐磨的表面处理(如ENIG - 化学镍金)有利于长期可靠性和多次测试。HASL(热风整平)也可以,但平整度和耐磨性不如ENIG。OSP(有机保焊膜)接触电阻可能较高且不耐多次测试。

* **平整度:** 测试点表面应尽量平整,避免凹凸不平影响接触。4. 电气和信号完整性考虑

* **隔离:** 高速信号线(如高速差分对、RF信号)上的测试点应谨慎添加,必要时需串联小电阻(如0欧姆或几欧姆)进行隔离,避免测试点引入的阻抗不连续或容性负载破坏信号质量。测试点应尽量从分支短线引出,而非直接串联在主走线上。

* **接地保护:** 对于敏感的模拟信号或高阻抗节点,可考虑在测试点附近增加接地保护环,减少干扰。

* **避免关键回路:** 不要在高速时钟环路、高速数据通路的核心路径上强行加测试点。

* **最小化引入电容/电感:** 测试焊盘和引线会增加额外的寄生参数。5. 可测试性设计原则

* **每个电气网络至少一个测试点:** 为了实现高覆盖率的ICT测试,理想情况下**每一个独立的电气网络(Net)** 都应有至少一个可探测的测试点。这是保证能检测开/短路的基础。

* **关键元件引脚直接访问:** 对于微处理器、FPGA、存储器等复杂IC,尽量保证其所有引脚或关键引脚都有直接访问的测试点,以便进行电源对地短路测试、IO状态测试、边界扫描等。

* **电源滤波电容两端:** 电源入口处的大容量滤波电容的两端(VCC和GND)都应设置测试点,便于测试电源网络及电容本身。

* **电阻/电容两端:** 用于检测开路的电阻或电容,其两端都需要有测试点。如果电阻一端接地或接电源,且该电源/地已有测试点,则该端可酌情省略。

* **边界扫描器件:** 为所有支持边界扫描的器件提供JTAG接口信号(TDI, TDO, TCK, TMS, TRST#)的测试点。TDI, TDO可能需要串联小电阻隔离(尤其当链路上有多个器件时)。

* **测试点冗余:** 对于非常关键的网络(如唯一的主电源、唯一的主时钟),可考虑设置冗余测试点以提高可靠性。

* **避免“一刀切”:** 测试策略(ICT为主?飞针为主?功能测试为主?边界扫描为主?)不同,对测试点的密度和位置要求也不同。需根据测试计划优化。6. 制造与组装考虑

* **防波峰焊遮盖:** 如果板子需要波峰焊,位于元件面(焊接面)的测试点必须被阻焊层覆盖(即不开窗),或者被选择性波峰焊托盘覆盖,以防止焊锡沾污。否则,测试点必须放在非波峰焊面(通常是顶面)。

* **贴片胶/红胶:** 避免测试点区域涂抹贴片胶。

* **丝印标识:**

* 为每个测试点添加清晰、唯一的标识(如 TP1, TP2, TP_VCC, TP_CPU_CLK),方便识别。丝印应靠近测试点但不覆盖它。

* 标注测试点的功能或网络名称。

* **定位孔:** 确保PCB上有高精度的定位孔(非电镀孔),用于测试夹具的精密定位。定位孔的位置和尺寸需符合夹具要求。7. 文件化

* 在PCB设计文件中(如Gerber、坐标文件、装配图)明确标注所有测试点的位置、编号和尺寸。

* 提供测试点列表(坐标、网络名、功能描述),供测试工程师编程夹具和测试程序使用。总结关键步骤

- 明确测试需求和策略: 首先确定要执行哪些测试(ICT? FCT? Boundary Scan? Flying Probe? AOI? X-Ray?),对覆盖率和成本的要求。

- 早期介入DFT: 在PCB布局布线阶段就开始规划测试点,而不是最后添加。与测试工程师和PCB设计师紧密沟通。

- 遵循物理放置规则: 严格遵守尺寸、间距、禁放区要求,确保可接触性。

- 覆盖关键网络: 确保电源、地、时钟、复位、关键控制信号、关键元件引脚、接口信号都有可访问的测试点。力争每个电气网络至少一个测试点。

- 考虑信号完整性: 对高速信号谨慎处理,必要时添加隔离电阻。

- 标识清晰: 添加丝印标识方便识别。

- 符合制造工艺: 考虑波峰焊等工艺对测试点位置的要求。

- 生成文档: 提供完整的测试点坐标和描述文件。

选择测试点是一个权衡的过程: 需要在测试覆盖率、测试成本(夹具成本、测试时间)、信号完整性、PCB空间限制、制造复杂度之间找到最佳平衡点。优秀的DFT设计能显著提高生产效率和产品质量,降低总体成本。

PCB板设计测试点的基本原则

线路板PCB测试点设置的原则是确保测试的准确性和高效性,同时避免对PCB板造成不必要的损害。以下是一些关键的设置原则: 1.测试点的分布:

2025-02-08 11:35:29

PCBA应力测试中MLCC失效应用和案例分析

在PCBA中,MLCC对应变比较敏感,过大的应力会导致PCBA失效。在生成过程中SMT,DIP,FATP三大电子制造环境,都会对PCBA产生应力

资料下载

![]() 应力测试仪

2022-03-21 11:19:43

应力测试仪

2022-03-21 11:19:43

电路板设计为什么要设置测试点?

对学电子的人来说,在电路板上设置测试点(test point)是在自然不过的事了,可是对学机械的人来说,测试点是什么?

资料下载

![]() 李伟

2022-02-10 09:32:59

李伟

2022-02-10 09:32:59

三星SM-G9600整机电路结构图及主要测试点详细数据资料免费下载

本文档的主要内容详细介绍的是SM-G9600整机电路结构图及主要测试点详细数据资料免费下载。

资料下载

![]() gaoxiangru

2019-05-29 08:00:00

gaoxiangru

2019-05-29 08:00:00

测试点对高速信号质量的影响

至于会不会影响信号质量就要看加测试点的方式和信号到底多快而定。基本上外加的测试点(不用在线既有的穿孔(via or DIP pin)当测试点)能

2022-09-16 08:55:35

在电路板上设置测试点?测试点是什么?

对学电子的人来说,在电路板上设置测试点(test point)是在自然不过的事了,可是对学机械的人来说,测试点是什么?基本上设置测试点的目的是为

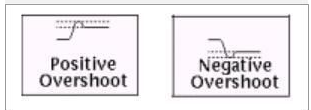

添加测试点对高速信号的质量影响概述!

问:添加测试点会不会影响高速信号的质量?答:至于会不会影响信号质量就要看加测试点的方式和信号到底多快而定。基本上外加的测试点(不用线上既有的穿孔

EDA教程:在PADS中添加表面型测试点

下拉框中选择需要的测试点类型,如TP_TOP,在右上角勾选PCBTopSide选项。3.点击工具栏中的DESIGN图标,然后选择添加测试点图标,

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机