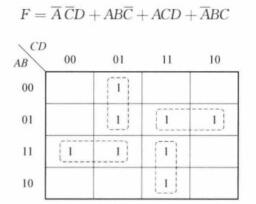

卡诺图

好的,卡诺图(Karnaugh Map,简称 K-Map)是一种用于简化布尔代数表达式(逻辑表达式)的图形工具。它特别适合于简化包含 2 到 6 个变量的逻辑函数。

以下是关于卡诺图的详细解释:

-

目的:

- 将复杂的真值表可视化。

- 识别并利用输入变量的组合中存在的逻辑相邻性(仅在一个变量上取值不同的组合)。

- 找到乘积项(与项)之和(SOP)或和项(或项)之积(POS)形式的最简表达式。 这通常意味着用最少的门电路(逻辑门)来实现所需的逻辑功能。

-

核心思想 - 相邻性:

- 卡诺图是一个二维网格(对于 2-4 个变量)或三维网格(5-6个变量),其关键特性是相邻的单元格(包括上下左右边缘和四角相连的单元格)在格雷码(Gray Code)的顺序上仅相差一个变量。

- 格雷码: 一种循环码,相邻的两个数之间只有一位二进制位不同。这是卡诺图布局的核心,确保几何上的相邻代表逻辑上的相邻。

- 正是这种仅相差一个变量的特性,使得相邻的单元格可以组合起来形成一个更简单的乘积项。

-

卡诺图的组成:

- 轴 (Axes):

- 图的顶部和左侧标示输入变量。

- 变量的值(通常是

0和1)按照 格雷码顺序 排列。例如,对于两个变量 A 和 B:- 顶部: B =

0, B =1 - 左侧: A =

0, A =1

- 顶部: B =

- 结果是一个 2x2 的网格。

- 单元格 (Cells):

- 网格中的每个小格子对应一个唯一的输入变量组合(最小项 minterm 或最大项 maxterm)。

- 在每个单元格中填入该输入组合对应的函数输出值

F(取自真值表)。这个值通常是:1: 表示该最小项使输出为真(对于 SOP 化简)。0: 表示该最小项使输出为假(也可用于 POS 化简)。X或-: 表示 无关项 (Don't Care),即输入组合在实际应用中不可能出现或者无论输出是0还是1都无关紧要的情况。无关项可以灵活地视作1或0,以帮助形成更大的组合圈,从而得到最简表达式。

- 轴 (Axes):

-

使用卡诺图进行化简(SOP 形式为例)的步骤:

- 根据变量数确定网格大小:

- 2 变量: 2x2 (4 单元格)

- 3 变量: 2x4 (8 单元格) 或 4x2 (8 单元格)

- 4 变量: 4x4 (16 单元格)

- 5/6 变量: 两个 4x4 网格堆叠 (较复杂)。

- 按格雷码顺序标记行列。

- 填入函数值: 根据真值表,将每个输入组合对应的输出值 (

1,0,X) 填入相应的单元格。 - 画组合圈 (Grouping):

- 圈出所有包含

1的单元格(要覆盖图中所有的1)。 - 圈的形状是矩形或正方形(在二维图中),大小为

1x1,1x2,1x4,2x2,2x4,4x4等(即大小为 2n 个单元格)。目标是圈尽可能少、尽可能大(覆盖的单元格尽可能多)。 - 可以跨越边界(上下、左右、四角被认为是相邻的)。

- 可以包含无关项 (

X),如果它们能帮助你形成一个更大或更少的圈(即把它们当作1)。 - 每个

1可以被多个圈圈住,但通常要避免不必要的重叠。

- 圈出所有包含

- 为每个圈写乘积项:

- 观察圈覆盖的范围(沿行方向和列方向)。

- 找出圈内取值保持不变的变量。

- 如果一个变量在该圈覆盖的所有单元格中取值都是

1,则在乘积项中包含该变量的原变量(如 A)。 - 如果一个变量在该圈覆盖的所有单元格中取值都是

0,则在乘积项中包含该变量的反变量(如 Ā 或 A')。 - 如果一个变量在该圈覆盖的单元格中既有

1又有0,则该变量不包含在该项中,它被消去了。

- 写出最简 SOP 表达式:

- 将每个圈对应的乘积项用或运算符 (+) 连接起来。

- 这就是化简后的布尔表达式(SOP 形式)。

- 根据变量数确定网格大小:

-

优点:

- 比纯代数运算(如布尔定理)更直观、更结构化、更不容易出错。

- 可以清晰看到最小化过程。

- 能有效处理无关项。

-

缺点/限制:

- 当变量数超过 6 个时,图形变得非常复杂且难以可视化,用起来很麻烦。

- 化简结果(画圈的方式)可能不是唯一的,但最简程度通常是相同的。

-

实际应用:

- 逻辑电路设计和优化(门电路最少化)。

- 简化组合逻辑电路。

- 数字系统设计(如编码器、译码器、数据选择器、比较器等)。

- 嵌入式系统设计和可编程逻辑器件(如 FPGA、CPLD)编程。

简单例子:

假设有一个三变量函数 (A, B, C),其卡诺图中包含 1 的单元格组成了一个 2x2 的方形圈。看图中:

- 沿 A 方向: 圈覆盖了 A=0 和 A=1 的行 => A 变化 => A 被消去。

- 沿 B 方向: 圈覆盖了 B=0 和 B=1 的行 => B 变化 => B 被消去。

- 沿 C 方向: 圈覆盖的单元格都在 C=0 的列(假设) => C 保持不变且为

0=> 写成 C'。 - 因此,这个

2x2的圈对应的化简项就是 C'。

总结:

卡诺图是一种基于网格的、利用输入变量的逻辑相邻性(通过几何相邻表示)来寻找布尔函数最简表达式的图形化工具。它通过画圈组合相邻的 1 和无关项 X,然后从圈中提取仅包含取值不变的变量的乘积项,最后将这些项相或(对于 SOP)或相与(对于 POS),达到化简逻辑表达式的目的。

是否需要看一个具体的卡诺图化简例子?

卡诺图在数字电路中的应用

卡诺图(Karnaugh map,简称K-map)在数字电路中具有广泛的应用,它主要用于布尔代数表达式的简化和最小化,从而优化数字电路的设计。以下是卡诺

2025-01-14 17:08:29

卡诺模型为人工智能领域提供了一种全新的视角

在探索人工智能如何更深层次满足用户需求、提升用户体验的旅程中,卡诺模型(Kano Model)提供了一个极具价值的理论框架。这一模型不仅为产品开发者带来了深刻的洞察力,同时也为人工智能领域的创新提供

2024-12-11 10:17:46

卡诺模型助力AI腾飞:人工智能发展新视角

在科技飞速发展的今天,人工智能(AI)已经成为引领未来社会变革的重要力量。然而,如何有效评估AI技术的成熟度和应用价值,一直是业界和学术界关注的焦点。卡诺模型作为一种成熟的技术成熟度评价工具,其在

2024-06-14 09:52:27

卡诺图如何化简

:SystemVerilog 从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。 今天更新整个关于卡诺图部分,数电忘记的,可以先回顾一下。

2022-11-01 09:02:25

卡诺普完成1亿元B轮融资 专注于研发更优质的机器人

国内机器人制造商「卡诺普」近期完成近亿元人民币B轮融资,由上海长江国弘投资管理有限公司旗下基金领投,国内某上市公司跟投。本轮融资将用于技术研发和行业拓展。此前,「卡诺普」曾获得来自北极光创投和苏州兴富的两轮融资,累计

2020-03-09 11:34:53

卡诺图化简画圈的原则和步骤

用代数法化简逻辑函数,需要依赖经验和技巧,有些复杂函数还不容易求得最简形式。卡诺图化简法是一种更加系统并有统一规则可循的逻辑函数化简法。

2020-03-06 13:58:27

卡诺普神转折 2019年是卡诺普机器人的“元年”

2020年1月9日,新年伊始,卡诺普第二届全球战略合作伙伴大会暨高峰论坛在“中国四大佛教名山”之一的峨眉完美收官。

2020-01-15 13:44:09

换一换

换一换

- 如何分清usb-c和type-c的区别

- 中国芯片现状怎样?芯片发展分析

- vga接口接线图及vga接口定义

- 芯片的工作原理是什么?

- 华为harmonyos是什么意思,看懂鸿蒙OS系统!

- 什么是蓝牙?它的主要作用是什么?

- ssd是什么意思

- 汽车电子包含哪些领域?

- TWS蓝牙耳机是什么意思?你真的了解吗

- 什么是单片机?有什么用?

- 升压电路图汇总解析

- plc的工作原理是什么?

- 再次免费公开一肖一吗

- 充电桩一般是如何收费的?有哪些收费标准?

- ADC是什么?高精度ADC是什么意思?

- EDA是什么?有什么作用?

- dtmb信号覆盖城市查询

- 中科院研发成功2nm光刻机

- 苹果手机哪几个支持无线充电的?

- type-c四根线接法图解

- 华为芯片为什么受制于美国?

- 怎样挑选路由器?

- 元宇宙概念股龙头一览

- 锂电池和铅酸电池哪个好?

- 什么是场效应管?它的作用是什么?

- 如何进行编码器的正确接线?接线方法介绍

- 虚短与虚断的概念介绍及区别

- 晶振的作用是什么?

- 大疆无人机的价格贵吗?大约在什么价位?

- 苹果nfc功能怎么复制门禁卡

- 单片机和嵌入式的区别是什么

- amoled屏幕和oled区别

- 复位电路的原理及作用

- BLDC电机技术分析

- dsp是什么意思?有什么作用?

- 苹果无线充电器怎么使用?

- iphone13promax电池容量是多少毫安

- 芯片的组成材料有什么

- 特斯拉充电桩充电是如何收费的?收费标准是什么?

- 直流电机驱动电路及原理图

- 传感器常见类型有哪些?

- 自举电路图

- 通讯隔离作用

- 苹果笔记本macbookpro18款与19款区别

- 新斯的指纹芯片供哪些客户

- 伺服电机是如何进行工作的?它的原理是什么?

- 无人机价钱多少?为什么说无人机烧钱?

- 以太网VPN技术概述

- 手机nfc功能打开好还是关闭好

- 十大公认音质好的无线蓝牙耳机