资料下载

如何设计适用于SoC片上系统的动态补偿与动态偏置LDO

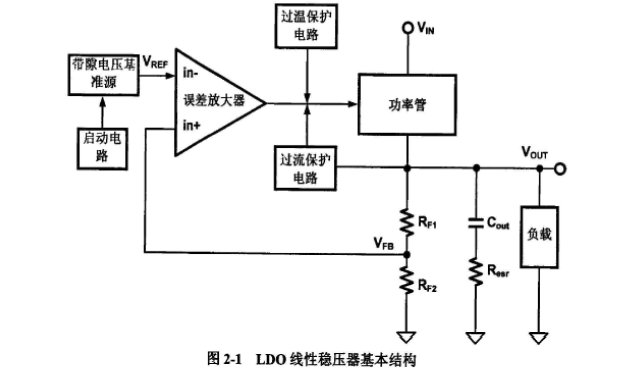

着便携设备的广泛应用,计算机、通讯和汽车等行业的迅速发展,电源管理类芯片技术不断发展。与DC-DC开关电压转换器相比,由于LDO具有成本低、电路结构简单、占用芯片面积小、低噪声和高纹波抑制能力等优点成为了电源管理芯片中的重要一员。而随着电子系统对电源要求的提高,传统的LDO已不能满足人们对芯片效率、噪声、精度、瞬态性能等指标的要求。因而,高性能LDO的研究成了电源管理芯片领域的研究热点。

本文设计了一款动态补偿、动态偏置、低静态电流、高精度、高电源抑制比的LDO。首先,详细分析LDO的关键性能指标,重点分析LDO的电源抑制比PSRR和线性调整率,阐述各指标间的折衷关系。然后,从频率角度分析研究控制环路极零点及稳定性补偿方法。针对LDO控制环路稳定性随负载电流变化的特点,在分析已有动态补偿策略优缺点的基础上给出一种新颖的动态补偿电路。这种补偿电路能很好地跟踪LDO输出端极点随负载电流的变化,从而使控制环路的稳定性几乎独立于负载电流的变化。最后,为消除大功率管栅极相关寄生电容对环路稳定性的影响,采用超级源极跟随器作为误差放大器之后的缓冲器,利用负反馈大大减小缓冲器输出阻抗。为改善环路的瞬态响应性能,设计了瞬态响应增强电路。

本设计采用CSMC0.5um工艺,利用Cadence的EDA工具完成电路晶体管级设计、前仿、物理版图设计和后仿,并完成流片测试,芯片面积为400um×650um。结果表明,本文设计的LDO工作电压为3.5V~6.5V,输出电压为3.3V,在提供100mA负载电流情况下电压差为200mV,负载瞬态变化时最大输出电压过冲为100mV,由电源电压变化和负载变化引起的输出电压误差分别为0.003%/V和0.005%/A,电源抑制比低频时为80dB,1kHz时为50dB,整个电路的静态电流约为34uA。上述结果表明该LDO基本达到设计指标,而且本文采用的动态补偿方案亦适用于SoC片上LDO的设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章