资料下载

×

正点原子FPGA静态时序分析与时序约束教程

消耗积分:3 |

格式:pdf |

大小:3.30 MB |

2020-11-11

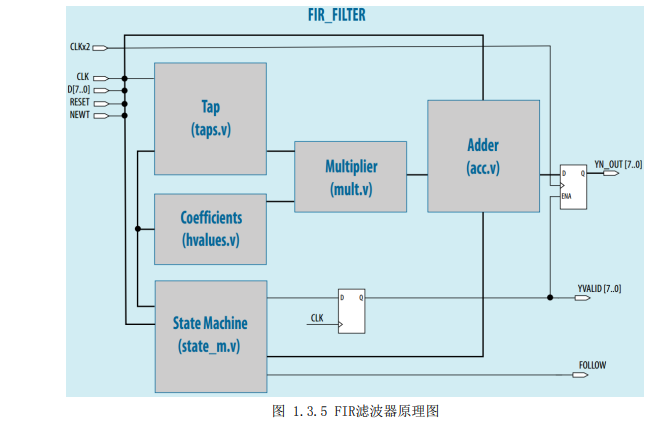

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

静态时序分析(Static Timing Analasis,STA)用来验证电路的性能,找到时序违规路径,并指导EDA工具对设计进行布局布线,以满足时序要求。静态时序分析的速度很快,但是它并不对电路的功能进行验证。时序约束(Timing Constraints)用来描述设计人员对时序的要求,比如时钟频率,输入输出的延时等。比如,对时钟频率的约束最简单的理解就是,设计者需要告诉EDA工具设计中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。 Intel Quartus软件中的时序分析工具TimeQuest Timing Analyzer使用工业标准的时序约束和分析方法,通过检查信号的到达时间是否符合约束所要求的时间,从而决定使设计正常工作所需要满足的时序关系。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章