资料下载

×

嵌入式RISC-V乱序执行处理器的设计方案

消耗积分:0 |

格式:rar |

大小:2.38 MB |

2021-03-11

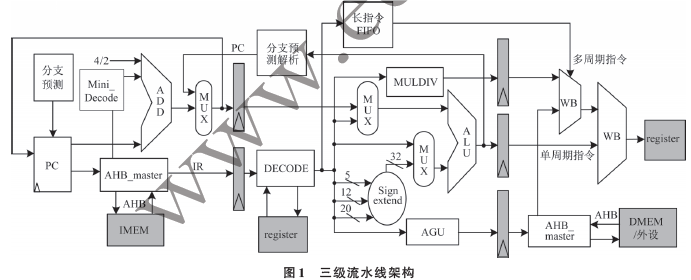

为满足嵌入式设备小面积高性能的需求,设计一种基于开源RISCⅤ指令集的32位可综合乱序处理器。处理器包括分支预测、相关性处理等关键技术,支持RISCⅤ基本整数运算、乘除法以及压缩指令集。采用具有顺序单发射、乱序执行、乱序写回等特性的三级流水线结构,运用哈佛体系结构及AHB总线协议,可满足并行访问指令与数据的需求。在 Artix-7(XC7A35T-L1CSG324FPGA开发板上以50MHz时钟频率完成功能验证,测试功耗为7.9mW。实验结果表明,在SMIC110nm的ASIC技术节点进综合分析,并在同等条件下与 ARM CortexM3等处理器进行对比,该系统面积减少64%,功耗降低0.57mW,可用手小面积低功耗的嵌入式领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章