关于MOSFET的开关特性你们了解多少

电子说

描述

MOSFET的开关特性解析|必看

MOS管最显著的特点也是具有放大能力。不过它是通过栅极电压uGS控制其工作状态的,是一种具有放大特性的由电压uGS控制的开关元件。

1、静态特性

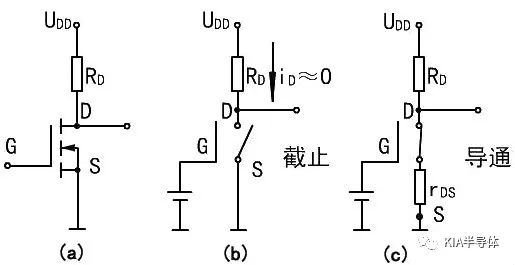

MOS管作为开关元件,同样是工作在截止或导通两种状态。由于MOS管是电压控制元件,所以主要由栅源电压uGS决定其工作状态。图下(a)为由NMOS增强型管构成的开关电路。

2、 漏极特性

反映漏极电流iD和漏极-源极间电压uDS之间关系的曲线族叫做漏极特性曲线,简称为漏极特性,也就是表示函数 iD=f(uDS)|uGS的几何图形,如图(a)所示。

当uGS为零或很小时,由于漏极D和源极S之间是两个背靠背的PN结,即使在漏极加上正电压(uDS》0V),MOS管中也不会有电流,也即管子处在截止状态。

当uGS大于开启电压UTN时,MOS管就导通了。因为在UGS=UTN时,栅极和衬底之间产生的电场已增加到足够强的程度,把P型衬底中的电子吸引到交界面处,形成的N型层——反型层,把两个N+区连接起来,也即沟通了漏极和源极。

所以,称此管为N沟道增强型MOS管。可变电阻区:当uGS》UTN后,在uDS比较小时,iD与uDS成近似线性关系,因此可把漏极和源极之间看成是一个可由uGS进行控制的电阻,uGS越大,曲线越陡,等效电阻越小,如图(a)所示。

恒流区(饱和区):当uGS》UTN后,在uDS比较大时,iD仅决定于uGS(饱和),而与uDS几乎无关,特性曲线近似水平线,D、S之间可以看成为一个受uGS控制的电流源。在数字电路中,MOS管不是工作在截止区,就是工作在可变电阻区,恒流区只是一种瞬间即逝的过度状态。

3、转移特性

反映漏极电流iD和栅源电压uGS关系的曲线叫做转移特性曲线,简称为转移特性,也就是表示函数 iD=f(uGS)|uDS的几何图形,如图(b )所示。当uGS《utn时,mos管是截止的。当ugs》UTN之后,只要在恒流区,转移特性曲线基本上是重合在一起的。曲线越陡,表示uGS对iD的控制作用越强,也即放大作用越强,且常用转移特性曲线的斜率跨导gm来表示。《/utn时,mos管是截止的。当ugs》

MOSFET开关power on 漏电问题

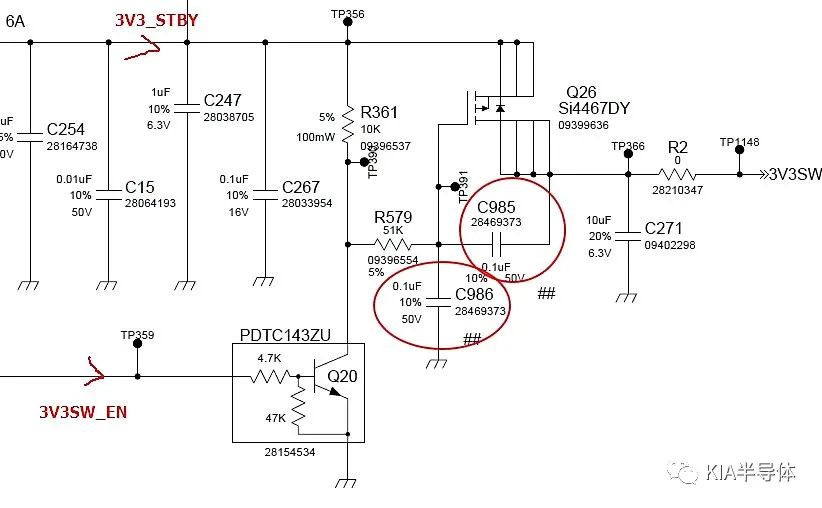

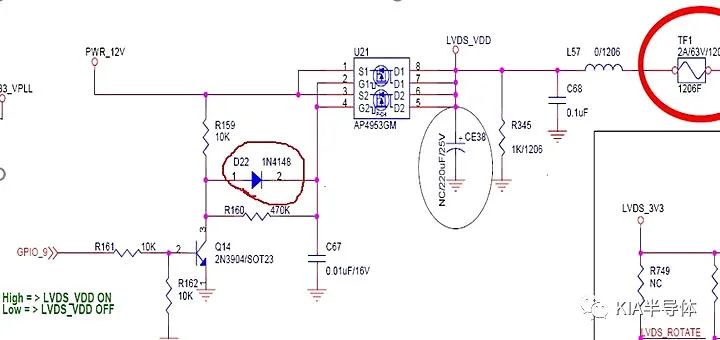

这是一个等电压转换开关。由单片机去控制从3V3STBY到3V3SW的pmos 开关。

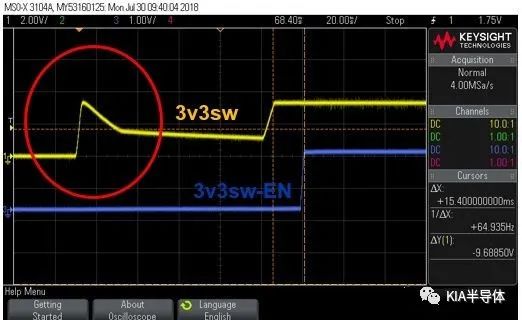

如下图,power on的过程中3V3SW power rail, 有一个voltage dip. 对比3V3SW_EN(blue),发现在turn on 控制信号到来之前,3V3SW上就有电压了。

示波器测量发现,3V3SW_EN控制信号pull high之前,mosfet gate电压(green)和3V3之间有1.1V左右的gap, 原则上在控制电压到来之前Vgate=3V3, 这样Vgs《Vth, mosfet不导通。

查阅mosfet 手册,Vth最小0.4V。由此可见,Vgs之间压差导致漏电。

去掉电路中的C986和C985之后,问题得到解决(最终方案C985换成了1nf的小电容)。

MOSFET的开关特性

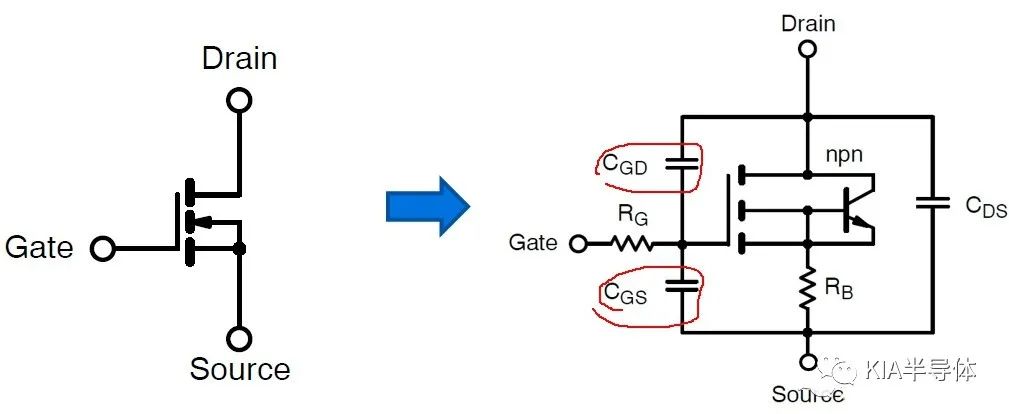

如下是mosfet的等效模型,Gate 和Drian、Source之间分别有寄生的电容Cgd和Cgs。这两个寄生电容直接影响着mosfet的开关特性。

有些mosfet手册上关于这两个寄生电容用Q来表示。

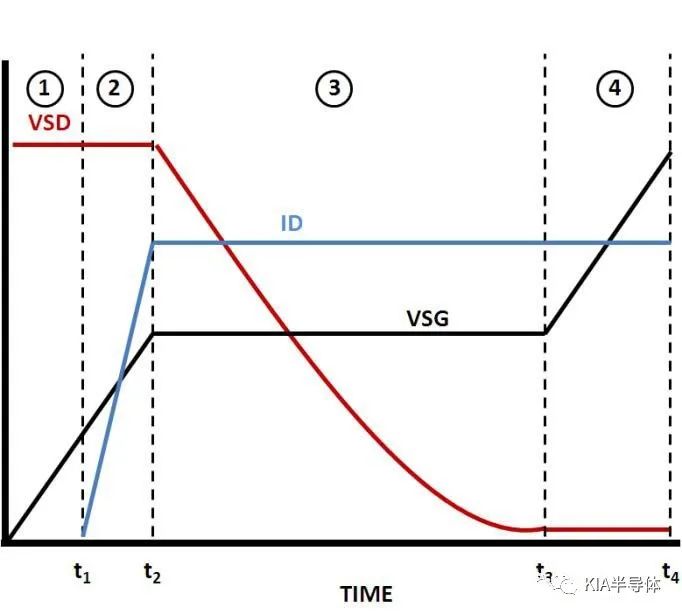

下图是MOSFET trun on的整个过程:

Total 分为4个区域

Region 1, VGS 开始增加,这个时候还没有到达Vth, 所以VSD保持不变,ID还是零。t1时刻,VGS=Vth

Region2, VGS 达到Vth以后, mosfet 开始导通,ID开始有电流。由于gate和source之间寄生电容的存在,gate的电压开始给Cgs充电,达到t2的时候,Cgs 冲满,VGS达到稳定值,ID达到最大。

Region3, VGS继续保持不变,Cgd开始充电,VSD之间的压差开始减少,到达t3的时候,Cgd充满了,VSD压差几乎到达最小值,这个时刻mosfet 完全导通。

Region4, VGS持续增大到驱动电压,VSD之间的压差=Rdson*ID.

从这个过程可以看到,如果要控制VSD的slew rate 可以控制region3的时间。Cgd增大,VSD slow rate就越小,当然in-rush current 也越小。

当然这也是为什么最上面的电路drain和gate之间有一个电容的原因,考虑到mosfet本身的寄生Cgd可能会比较小,增加这样一个电容可以控制开关的slew rate。

回到上面的问题,由于电路中C985 C986都放了0.1uf,比较大,3V3STBY上升的过程中Gate电平没有快速达到3.3V,导致漏电。减少容值,可解决问题。

在有些电路中为了避免上述问题,可以加一个二极管快速导通使gate电压快速达到和source一致。

编辑:jq

- 相关推荐

- MOSFET

-

功率MOSFET的阻性负载开关特性2016-12-16 0

-

MOSFET的开关特性及其温度特性2018-11-28 0

-

MOSFET特性2019-04-10 0

-

萌新求助,请大神介绍一下关于MOSFET的栅极/漏极导通特性与开关过程2021-04-14 0

-

了解MOSFET的一些原理2021-09-13 0

-

基于漏极导通区MOSFET开关过程解读2011-09-14 1009

-

基于漏极导通区特性理解mosfet开关过程资料下载.pdf2018-05-10 1036

-

MOSFET的原理及开关特性分析2019-04-19 5217

-

MOSFET的阈值、ID-VGS特性及温度特性2023-02-09 5356

-

关于IGBT/MOSFET/BJT的开关工作特性2023-02-23 249

-

Nexperia | 了解RET的开关特性2023-05-24 483

-

探究快速开关应用中SiC MOSFET体二极管的关断特性2023-01-04 1338

-

MOSFET漏极导通特性与开关过程简析2023-12-04 663

全部0条评论

快来发表一下你的评论吧 !