这是 A2O POWER 处理器核心 RTL 和相关的 FPGA 实现(使用 ADM-PCIE-9V3 FPGA)的发布。

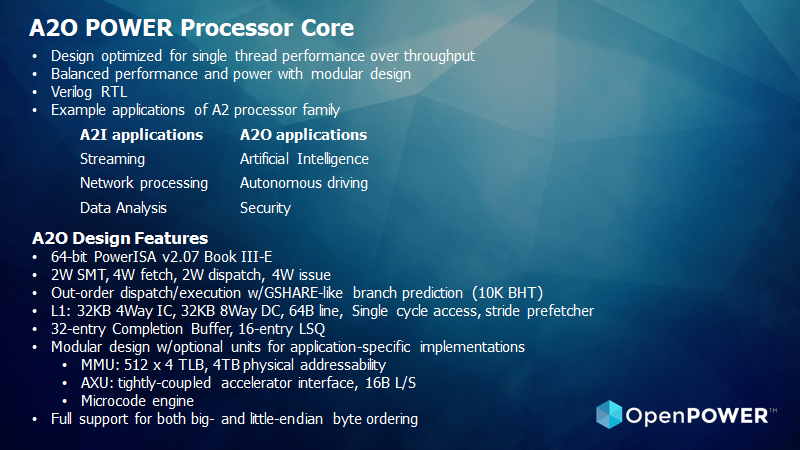

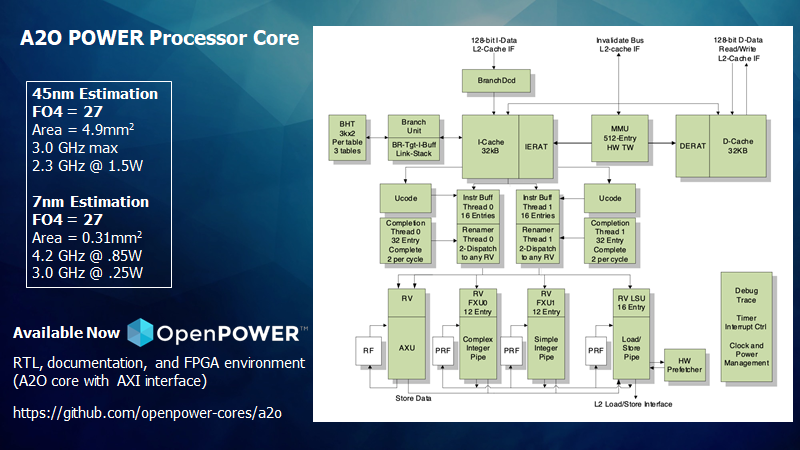

A2O 核心是为了优化单线程性能而诞生的,目标是 45nm 技术的 3+GHz。它是一个 27 FO4 的实现,有一个支持 1 或 2 个线程的外序管道。它完全支持使用 Book III-E 的 Power ISA 2.07。该内核还被设计成支持 MMU 和 AXU 逻辑宏的可插拔实现。这包括取消 MMU 和使用 ERAT-only 模式进行翻译/保护。

A2O设计是A2I的后续设计,用Verilog编写,支持的线程数比A2I少,但每个线程的性能更高,使用了无序执行(寄存器重命名、保留站、完成缓冲区)和存储队列。两个核心的A2L2外部接口基本相同。

FPGA Implementation Notes

- 有许多旋钮可用于调整生成参数。很少做实验来测试它们是否有效,或者对面积的影响等等。

- 到目前为止,仅完成了单线程生成。使用中的FPGA,一个线程的利用率非常高。

- A2I使用clk_1x和clk_2x(对于某些特殊数组),但是A2O也使用clk_4x。这(可能还伴随着区域拥塞)导致将clk_1x更改为50MHz,以减轻时序压力(建立和保持未命中)。