资料下载

×

基于FPGA的真随机数发生器设计

消耗积分:0 |

格式:pdf |

大小:575 KB |

2011-05-30

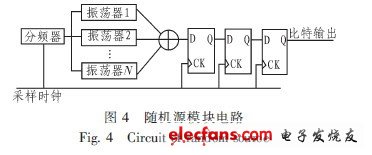

设计并实现了一种基于FPGA的真随机数发生器,利用一对振荡环路之间的相位漂移和抖动以及亚稳态作为随机源,使用线性反馈移位寄存器的输出与原始序列运算作为后续处理。在Xilinx Virtex-5平台的测试实验中,探讨了振荡器数量以及采样频率等参数对随机序列的统计特性的影响。测试结果表明本设计产生的随机序列能够通过DIEHARD测试,性能满足要求。由于仅使用了普通逻辑单元,使得本设计能够迅速移植到ASIC设计,大大缩短了开发周期。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章