资料下载

使用Tensil、TF-Lite和PYNQ在Ultra96板上运行YOLO v4 Tiny

描述

介绍

本教程将使用Avnet Ultra96 V2开发板和Tensil 开源推理加速器来展示如何在 FPGA 上运行YOLO v4 Tiny——最先进的目标检测机器学习模型。本教程参考之前的Ultra96教程有关生成 Tensil RTL 和让Xilinx Vivado合成比特流的分步说明。

如果您遇到问题或发现错误,您可以在我们的Discord上提问或发送电子邮件至support@tensil.ai。

概述

在开始之前,让我们鸟瞰一下我们想要完成的任务。我们将按照以下步骤操作:

- 生成和合成 Tensil RTL

- 为 Tensil 编译 YOLO v4 Tiny 模型

- 准备 PYNQ 和 TF-Lite

- 使用 PYNQ 执行

1.生成和合成Tensil RTL

第一步,我们将使用 Tensil 工具生成 RTL 代码,然后使用 Xilinx Vivado 为 Ultra96 板合成比特流。由于此过程与其他 Ultra96 教程相同,因此我们建议您参考 ResNet20 教程中的第 1 至第 4 节。

或者,您可以跳过此步骤并下载现成的比特流。为此,我们在后续部分中包含说明。

2. 为 Tensil 编译 YOLO v4 Tiny 模型

现在,我们需要将 ML 模型编译为由 TCU 硬件直接执行的 TCU 指令组成的 Tensil 二进制文件。YOLO v4 Tiny 模型包含在 192 和 416 两种分辨率中,位于 和 的 Tensil 泊坞窗图像/demo/models/yolov4_tiny_192.onnx中/demo/models/yolov4_tiny_416.onnx。更高的分辨率将使用更多的计算来检测更小的对象,因此每秒的帧数更少。请注意,下面我们将使用 192 分辨率,但只需将其替换为 416 也可以。

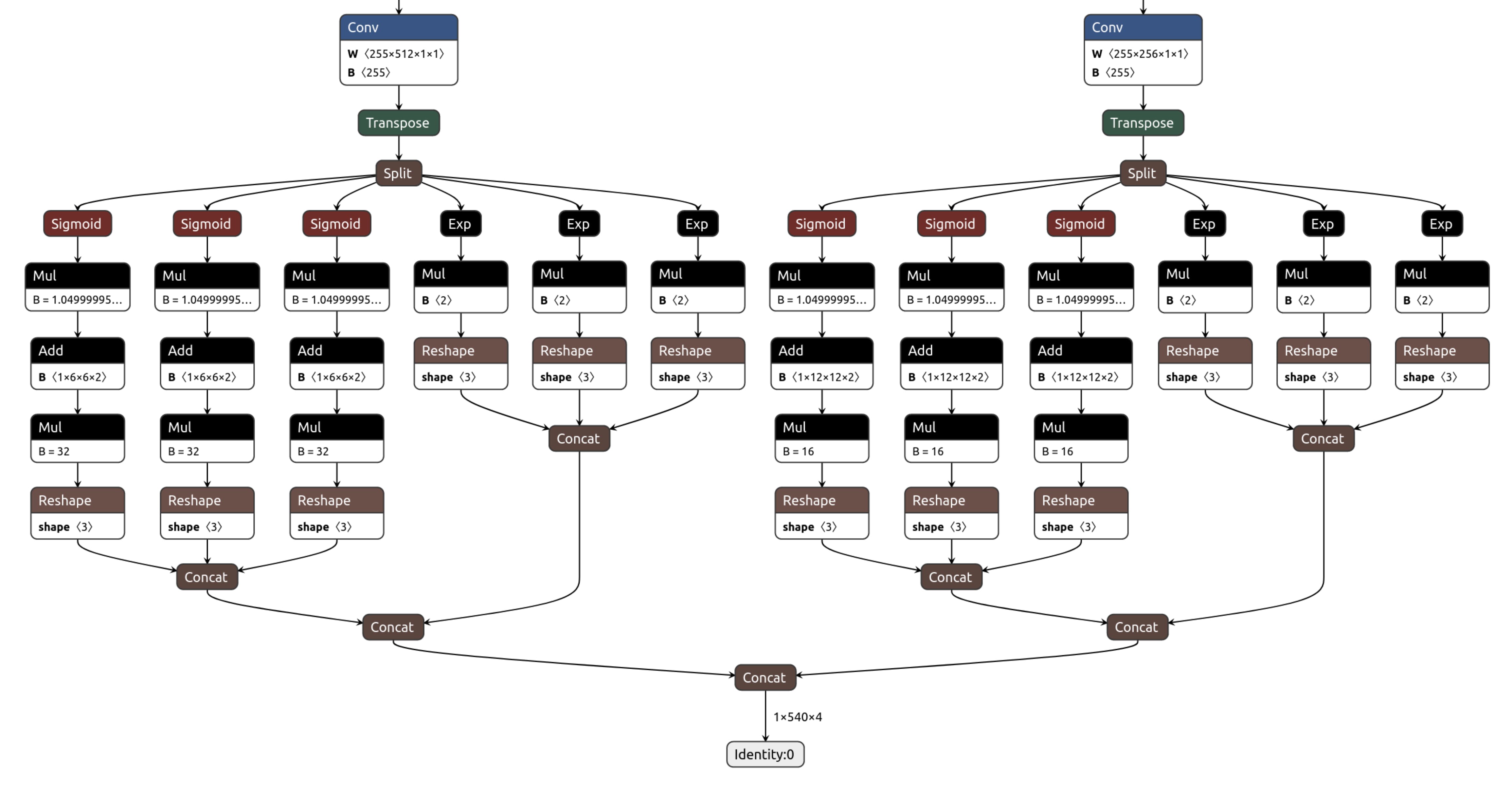

正如我们在介绍中提到的,我们将使用 TF-Lite 框架来运行 YOLO v4 Tiny 的后处理。具体来说,此后处理包括 Tensil 硬件不支持的操作Sigmoid。Exp(我们计划使用基于泰勒展开的表查找来实现它们。)这意味着对于 Tensil,我们需要编译以最后一个卷积层结尾的模型。在这些层之下,我们需要编译 TF-Lite 模型。要识别 Tensil 编译器的输出节点,请查看Netron 中的模型。

最后两个卷积操作的输出名为model/conv2d_17/BiasAdd:0和model/conv2d_20/BiasAdd:0。

如果你一路走来,那么恭喜你!通过尝试自己的模型和架构,您已准备好将事情提升到一个新的水平。加入我们的Discord打个招呼并提出问题,或发送电子邮件至support@tensil.ai。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章