全方位理解功率MOSFET的雪崩失效现象

电子说

描述

1 引言

功率MOSFET在电力电子设备中应用十分广泛,因其故障而引起的电子设备损坏也比较常见。分析研究功率MOSFET故障的原因、后果,对于MOSFET的进一步推广应用具有重要意义。

其中MOSFET的雪崩击穿失效导致的故障是功率MOSFET比较典型的故障之一。本文就对功率MOSFET雪崩击穿的特性,以及在电源案例中的典型故障进行了简单的分析,来全方位的理解功率MOSFET的雪崩失效现象。

2 功率MOSFET雪崩击穿理论分析

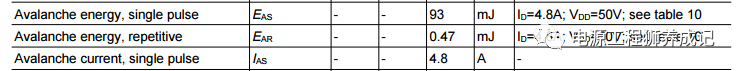

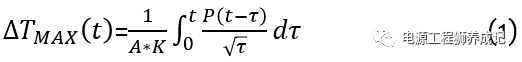

在功率MOSFET雪崩分析之前,需要对数据手册中的相关参数进行说明。一般数据手册中包含如下图所示的单脉冲雪崩能量EAS、重复脉冲雪崩能量EAR、单次脉冲雪崩电流IAS等。这些参数反映了该功率MOSFET的雪崩能力。

图1 MOSFET的相关雪崩参数

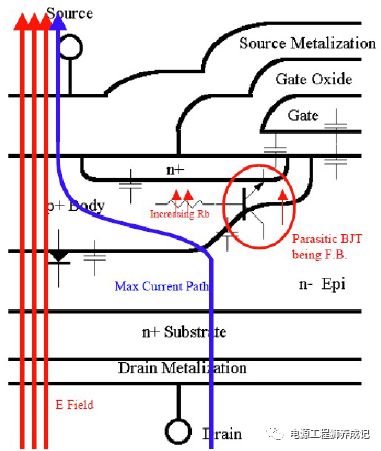

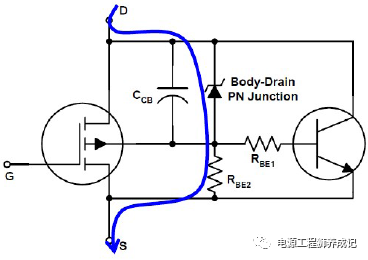

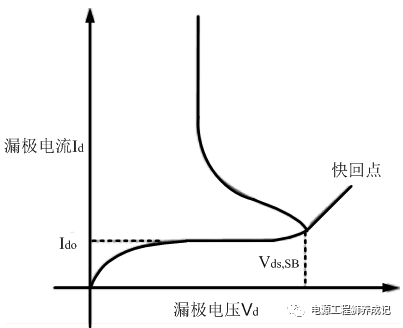

图2为MOSFET的体内等效电路,阐述了雪崩击穿的原因。其中含有一个寄生的双极性晶体管V2,它的集电极、发射极同时也是MOSFET的漏极和源极。当MOSFET漏极存在大电流Id,高电压Vd时,器件内电离作用加剧,出现大量的空穴电流,经Rb流入源极,导致寄生三极管基极电势Vb升高,出现所谓的“快回(Snap- back) ”现象,即在Vb升高到一定程度时,寄生三极管V2导通,集电极(即漏极)电压快速返回达到晶体管基极开路时的击穿电压(增益很高的晶体管中该值相对较低),从而发生雪崩击穿,如图2所示。

(a) 功率MOSFET体内等效电路图

(b) 外部分析电路

图2 MOSFET 等效电路

图3 雪崩击穿时I -V 曲线

3 功率 MOSFET 雪崩击穿的微观分析

双极性器件在发生二次击穿时,集电极电压会在故障瞬间很短时间内(可能小于1ns)衰减几百伏。这种电压锐减主要是由雪崩式注入引起的, 主要原因在于:二次击穿时, 器件内部电场很大, 电流密度也比较大, 两种因素同时存在, 一起影响正常时的耗尽区固定电荷,使载流子发生雪崩式倍增。

对于不同的器件,发生雪崩式注入的情况是不同的。对于双极性晶体管,除了电场应力的原因外, 正向偏置时器件的热不稳定性, 也有可能使其电流密度达到雪崩式注入值。而对于MOSFET,由于是多数载流子器件,通常认为其不会发生正向偏置二次击穿,而在反向偏置时, 只有电气方面的原因能使其电流密度达到雪崩注入值, 而与热应力无关。以下对功率MOSFET 的雪崩击穿作进一步的分析。

如图2所示,在MOSFET 内部各层间存在寄生二极管、晶体管(三极管)器件。从微观角度而言,这些寄生器件都是器件内部 PN 结间形成的等效器件,它们中的空穴、电子在高速开关过程中受各种因素的影响,会导致MOSFET 的各种不同的表现。

导通时,正向电压大于门槛电压,电子由源极经体表反转层形成的沟道进入漏极,之后直接进入漏极节点;漏极寄生二极管的反向漏电流会在饱和区产生一个小的电流分量。而在稳态时,寄生二极管、晶体管的影响不大。

关断时,为使MOSFET体表反转层关断,应当去掉栅极电压或加反向电压。这时,沟道电流 (漏极电流)开始减少, 感性负载使漏极电压升高以维持漏极电流恒定。漏极电压升高,其电流由沟道电流和位移电流(漏极体二极管耗尽区生成的,且与dVDS /dt成比例)组成。漏极电压升高的比率与基极放电以及漏极耗尽区充电的比率有关;而后者是由漏-源极电容、漏极电流决定的。在忽略其它原因时,漏极电流越大电压会升高得越快。

如果没有外部钳位电路,漏极电压将持续升高,则漏极体二极管由于雪崩倍增产生载流子,而进入持续导通模式(Sustaining Mode)。此时,全部的漏极电流(此时即雪崩电流)流过体二极管,而沟道电流为零。由上述分析可以看出,可能引起雪崩击穿的三种电流为漏电流、位移电流(即dVDS/dt电流)、雪崩电流,三者理论上都会激活寄生晶体管导通。寄生晶体管导通使MOSFET由高压小电流迅速过渡到低压大电流状态,从而发生雪崩击穿。

4 雪崩击穿时能量与温度的变化

在开关管雪崩击穿过程中,能量集中在功率器件各耗散层和沟道中,在寄生三极管激活导通发生二次击穿时,MOSFET会伴随急剧的发热现象,这是能量释放的表现。以下对雪崩击穿时能量耗散与温升的关系进行分析。

雪崩击穿时的耗散能量与温升的关系为

其中,A是硅片面积,K常数与硅片的热性能相关。

而雪崩能量为

由上述公式可以看出,在功率MOSFET发生雪崩击穿时,器件温度与初始功率,以及器件本身的性能有关。在雪崩击穿后如果没有适当的缓冲、抑制措施, 随着电流的增大,器件发散内部能量的能力越来越差, 温度上升很快, 很可能将器件烧毁。

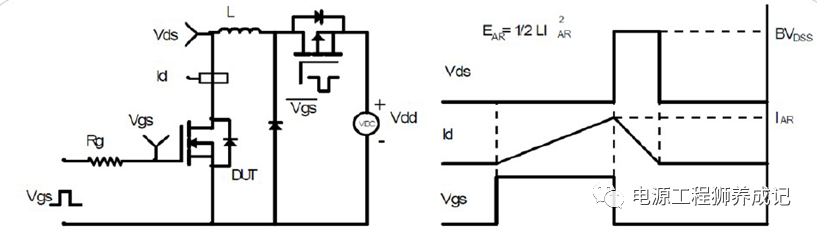

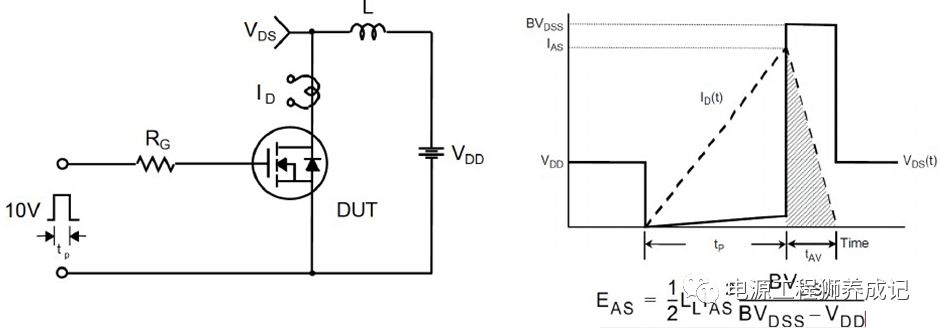

5 雪崩能量的测量

雪崩能量通常在非钳位感性开关UIS条件下测量,通常包括二组值:单脉冲雪崩能量EAS和单脉冲雪崩电流IAS,重复脉冲雪崩能量EAR和重复脉冲雪崩电流IAR。单脉冲雪崩能量和雪崩电流的测试的电路有二种:去耦的EAS测量电路和非去耦的EAS测量电路,如图4、图5所示。

图4 去耦的EAS测量电路

图5 非去耦的EAS测量电路

对于一些中、低压的器件,VDS - VDD变得很小,使用非去耦电路测量会产生较大的差异,因此对于中、低压的功率MOSFET,通常使用去耦的EAS测量电路。

在去耦的EAS测量电路中,当测试的功率MOSFET和控制管同时关断时,由于MOSFET的D、S之间有寄生电容CDS,因此在二极管导通续流时,电感L和CDS形成谐振回路,L的电流降低使CDS上的电压上升,直到电感的电流为0时,续流二极管D自然关断,电感L中储存的能量应该全部转换到CDS中。

如果电感L=0.1mH,IAS=10A,CDS=1nF,理论上,电压VDS为:

得VDS=3100V。

这样高的电压值是不可能的,那么为什么会有这样的情况?从实际的工作原理来看,MOSFET的D、S内部相当于一个反并联的二极管。当这个二极管两端加上反向电压,因此其工作在反向工作区,随着VDS增加,高过BVDSS,增加到接近于对应二极管的钳位电压时,VDS的电压就不会再明显的增加,而是维持在钳位电压值基本不变。此时,MOSFET工作于雪崩区,最大的平台钳位电压就是雪崩电压。

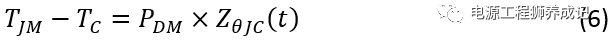

为了保障MOSFET工作在雪崩区不失效,还必须考虑MOSFET的雪崩能量与温升的关系,

比如在去耦的EAS测试电路中,单次雪崩能量为

雪崩功率为

结合式(2), (4), (5)可以得出雪崩功率,再由式(6)即可估算出MOSFET的节温的温升。

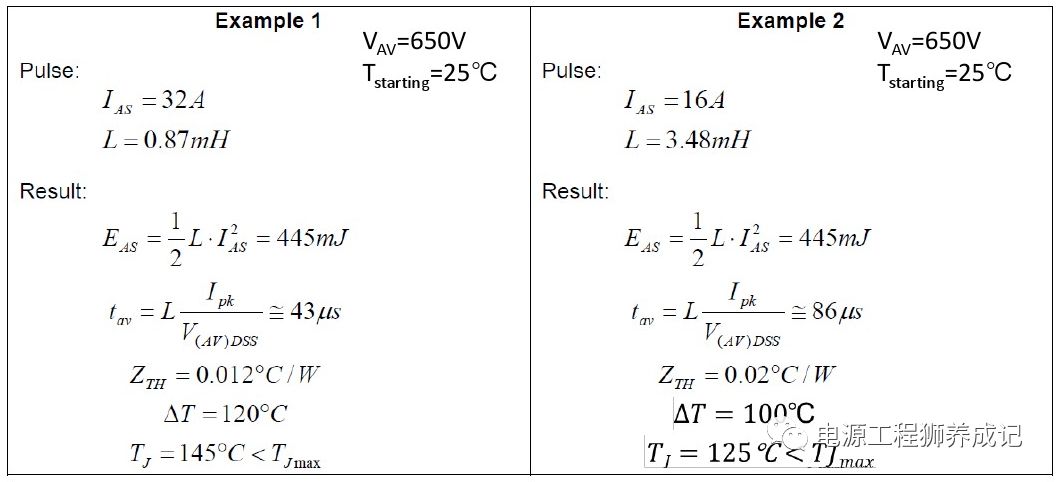

图6给出了两个不同的估算结果,差异还是比较大的,所以具体应用时,应以具体的条件参数估算温升,防止过温损坏。

图6 不同测试条件下的温升测试结果

6 雪崩能量的失效机理

功率MOSFET的雪崩损坏有三种模式:热损坏、寄生三极管导通损坏和VGS尖峰误触发导通损坏。

1) 热损坏

功率MOSFET在功率脉冲的作用下进入雪崩的工作状态,VDS电压增加,体到epi-结的电场也增加,当场强增加到临界值时(硅中大约为300kV/cm),产生载流子的雪崩倍增,导致电流突然急剧增加。雪崩倍增并不是一个损坏的过程,在这个过程中,由于功耗增加导致硅片的结温升高,当结温升高到硅片特性允许的临界值,失效将发生。

2) 寄生三极管导通损坏

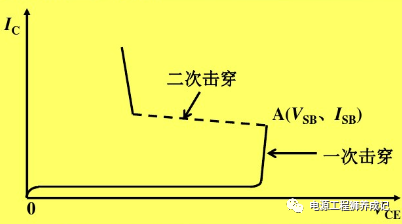

前文已详细分析了雪崩现象的产生。寄生三极管的失效分为热击穿和二次击穿,如图7所示。

热击穿:耗散功率转化为热,使集电结结温升高,集电结结电流进一步增大,使三极管烧毁。

二次击穿:局部大电流导致三极管烧通,使VCE击穿电压急剧降低,IC电流增大,使三极管烧毁。

图7 寄生三极管雪崩失效

3) VGS尖峰误触发导通损坏

功率MOSFET在雪崩过程中硅片的温度升高,VGS的阈值急剧降低,同时在雪崩过程中,VDS的电压耦合到G极,在G、S上产生的电压VGS高于的阈值,MOSFET误触发而开通,导致瞬态的大电流流过硅片局部区域,产生电流熔丝效应,从而损坏功率MOSFET,在这个过程中,通常也会叠加寄生三极管导通的损坏机理。在实际应用中,UIS雪崩较少以这种方式发生失效。

7 雪崩能量的应用与预防措施

在实际的应用中,雪崩的损坏常发生在过压过流高温等极端条件下。如高温下,系统输出短路及过载测试,输入过电压测试以及动态的老化测试中,MOSFET的损坏需要考虑雪崩能量导致的击穿。

MOSFET的电压尖峰产生时,例如反激应用,MOSFET关断时会产生较大的电压尖峰:VIN+输出反射电压+漏感,这时需要考虑雪崩能量,必要时,需加一些防护措施(加钳位电路),保证MOSFET不被损坏。

发生在电感上的没有预料到的瞬态电压,如输出短路时,变压器原边电感饱和,引起瞬态大电流的变化,器件需要考虑雪崩击穿的可能。相应的预防措施有a) 加开短路的系统响应,以降低漏极电流;b) 优化电路以及变压器设计,减小漏感和线路杂散电感;c) 加缓冲电路抑制di/dt.

8 总结

本文阐述和分析了MOSFET的雪崩现象的相关问题,包括雪崩击穿的理论分析,雪崩能量以及温升的关系,雪崩能量的测量和应用中如何考虑雪崩现象和相关的预防措施。今后在工作中可以针对MOSFET的使用以及失效时有一个更明确的认识和分析,给出更具有针对性的措施。

-

全方位距离雷达动态检测系统的设计怎么设计2014-03-06 0

-

功率MOSFET重复雪崩电流及重复雪崩能量2017-09-22 0

-

MOSFET的UIS及雪崩能量解析2010-04-26 5777

-

【转帖】MOSFET失效的六点总结2018-08-15 0

-

MOSFET的失效机理 —总结—2022-07-26 0

-

功率MOSFET雪崩击穿问题分析2009-07-06 5614

-

如何理解功率MOSFET规格书之雪崩特性和体二极管参数的详细资料说明2020-03-07 1222

-

雪崩下SiC MOSFET应用技术的鲁棒性评估2020-08-09 1775

-

MOSFET的失效机理:什么是雪崩失效2023-02-13 1496

-

MOSFET的失效机理:dV/dt失效和雪崩失效2023-04-15 1105

-

功率MOSFET的雪崩强度限值2023-05-15 1422

-

什么是MOSFET雪崩失效2023-12-06 376

-

功率MOSFET雪崩特性分析2023-12-04 417

-

MOSFET雪崩击穿图解 MOSFET避免雪崩失效的方法2024-02-25 1652

-

雪崩失效的原因 雪崩能量的失效机理模式2024-02-25 770

全部0条评论

快来发表一下你的评论吧 !