隔离式DC/DC变换器的电磁干扰源机理

EMC/EMI设计

描述

进行开关电源的电磁兼容性设计时 ,首先进行一个系统设计 , 明确以下几点:

1. 明确系统要满足的电磁兼容标准;

2. 确定系统内的关键电路部分 ,包括强干扰源电路、高度敏感电路;

3. 明确电源设备工作环境中的电磁干扰源及敏感设备;

4. 确定对电源设备所要采取的电磁兼容性措施。

一、DC/DC变换器内部噪声干扰源分析

1.二极管的反向恢复引起噪声干扰

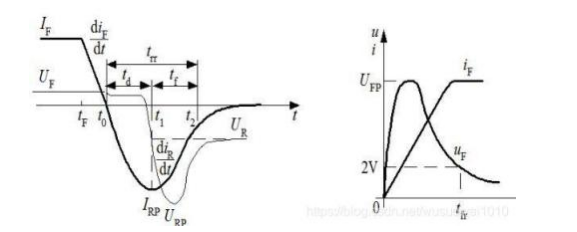

在开关电源中常使用工频整流二极管、高频整流二极管、续流二极管等 , 由于这些二极管都工作在开关状态 ,如图所示 ,在二 极管由阻断状态到导通工作过程中 ,将产生一个很高的电压尖峰VFP;在二极管由导通状态到阻断工作过程中 ,存在一个反向 恢复时间trr,在反向恢复过程中 , 由于二极管封装电感及引线电感的存在 ,将产生一个反向电压尖峰VRP, 由于少子的存储与 复合效应 ,会产生瞬变的反向恢复电流IRP,这种快速的电流、电压突变是电磁干扰产生的根源。

电流电压波形图

二极管反向恢复时电流电压波形 二极管正向导通电流电压波形

2.开关管开关动作时产生电磁干扰

二极管反向恢复时电流电压波形 二极管正向导通电流电压波形

在正激式、推挽式、桥式变换器中 ,流过开关管的电流波形在阻性负载时近似矩形波 ,含有丰富的高频成分 ,这些高频谐波会 产生很强的电磁干扰 ,在反激变换器中 ,流过开关管的电流波形在阻性负载时近似三角波 ,高次谐波成分相对较少 。开关管在 开通时 , 由于开关时间很短以及逆变回路中引线电感的存在 ,将产生很大的dV/dt突变和很高的尖峰电压 ,在开关管的关断

时 , 由于关断时间很短 ,将产生很大的di/dt突变和很高的电流尖峰 ,这些电流、电压突变将产生很强的电磁干扰。

3. 电感、变压器等磁性元件引起的电磁干扰:在开关电源中存在输入滤波电感、功率变压器、隔离变压器、输出滤波电感等 磁性元件 , 隔离变压器初次级之间存在寄生电容 ,高频干扰信号通过寄生电容耦合到次边;功率变压器由于绕制工艺等原因 , 原次边耦合不理想而存在漏感 ,漏电感将产生电磁辐射干扰 ,另外功率变压器线圈绕组流过高频脉冲电流 ,在周围形成高频电 磁场; 电感线圈中流过脉动电流会产生电磁场辐射 ,而且在负载突切时 ,会形成电压尖峰 , 同时当它工作在饱和状态时 ,将会 产生电流突变 ,这些都会引起电磁干扰。

4.控制电路中周期性的高频脉冲信号如振荡器产生的高频脉冲信号等将产生高频高次谐波 ,对周围电路产生电磁干扰。

5.此外电路中还会有地环路干扰、公共阻抗耦合干扰 , 以及控制电源噪声干扰等。

6.开关电源中的布线设计非常重要 ,不合理布线将使电磁干扰通过线线之间的耦合电容和分布互感串扰或辐射到邻近导线 上 ,从而影响其它电路的正常工作。

7.热辐射产生的电磁干扰 ,热辐射是以电磁波的形式进行热交换 ,这种电磁干扰影响其它电子元器件或电路的正常稳定工 作。

二、外界的电磁干扰

对于某一 电子设备 ,外界对其产生影响的电磁干扰包括: 电网中的谐波干扰、雷电、太阳噪声、静电放电 , 以及周围的高频发 射设备引起的干扰。

三、电磁干扰的后果

电磁干扰将造成传输信号畸变 ,影响设备的正常工作 。对于雷电、静电放电等高能量的电磁干扰 ,严重时会损坏设备 。而对于 某些设备 , 电磁辐射会引起重要信息的泄漏。

四、开关电源的电磁兼容设计

了解了开关电源内部及外部电磁干扰源后 ,我们还应知道 ,形成电磁干扰机理的三要素是还有传播途径和受扰设备 。因此开关 电源的电磁兼容设计主要从以下三个方面入手: 1,减小干扰源的电磁干扰能量;2,切断干扰传播途径;3,提高受扰设备的 抗干扰能力。

正确了解和把握开关电源的电磁干扰源及其产生机理和干扰传播途径 ,对于采取何种抗干扰措施以使设备满足电磁兼容要求非 常重要 。由于干扰源有开关电源内部产生的干扰源和外部的干扰源 ,而且可以说干扰源无法消除 ,受扰设备也总是存在 , 因此 可以说电磁兼容问题总是存在。

下面以隔离式DC/DC变换器为例 ,讨论开关电源的电磁兼容性设计:

1. DC/DC变换器输入滤波电路的设计

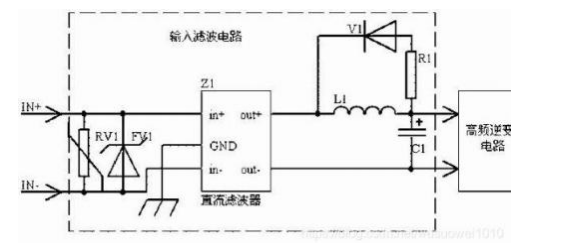

如图所示 ,FV1为瞬态电压抑制二极管 ,RV1为压敏电阻 ,都具有很强的瞬变浪涌电流的吸收能力 ,能很好的保护后级元件或 电路免遭浪涌电压的破坏 。Z1为直流EMI滤波器 ,必须良好接地 ,接地线要短 ,最好直接安装在金属外壳上 ,还要保证其输 入、输出线之间的屏蔽隔离 ,才能有效的切断传导干扰沿输入线的传播和辐射干扰沿空间的传播 。L1、C1组成低通滤波电

路 , 当L1电感值较大时 ,还需增加如图所示的V1和R1元件 ,形成续流回路吸收L1断开时释放的电场能 ,否则L1产生的电压尖 峰就会形成电磁干扰 , 电感L1所使用的磁芯最好为闭合磁芯 ,带气隙的开环磁芯的漏磁场会形成电磁干扰 ,C1的容量较大为 好 ,这样可以减小输入线上的纹波电压 ,从而减小输入导线周围形成的电磁场。

DC/DC变换器输入滤波电路

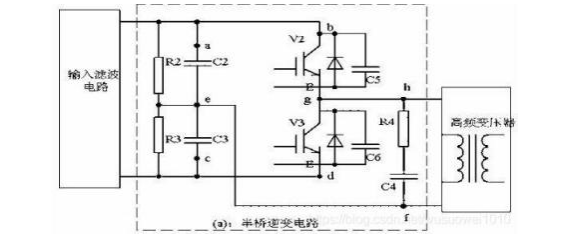

2.高频逆变电路的电磁兼容设计 ,如图所示 ,C2、C3、V2、V3组成的半桥逆变电路 ,V2、V3为IGBT、MOSFET等开关元件 , 在V2、V3开通和关断时 , 由于开关时间很快以及引线电感、变压器漏感的存在 , 回路会产生较高的di/dt、dv/dt突变 ,从而形成 电磁干扰 ,为此在变压器原边两端增加R4、C4构成的吸收回路 ,或在V2、V3两端分别并联电容器C5、C6,并缩短引线 ,减

小ab、cd、gh、ef的引线电感 。在设计中 ,C4、C5、C6一般采用低感电容 , 电容器容量的大小取决于引线电感量、回路中电流 值以及允许的过冲电压值的大小 ,LI2/2=C△V2/2公式求得C的大小 ,其中L为回路电感 ,I为回路电流 ,△V为过冲电压值。

为减小△V,就必须减小回路引线电感值 ,为此在设计时常使用一种叫“多层低感复合母排”的装置 , 由我所申请专利的该种母 排装置能将回路电感降低到足够小 ,达10nH级 ,从而达到减小高频逆变回路电磁干扰的目的。

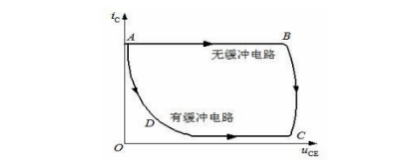

开关管电流、电压波形比较图

从电磁兼容性设计角度考虑 ,应尽量降低开关管V2、V3的开关频率 ,从而降低di/dt、dv/dt值 。另外使用ZCS或ZVS软开关变换 技术能有效降低高频逆变回路的电磁干扰 。在大电流或高电压下的快速开关动作是产生电磁噪声的根本 , 因此尽可能选用产生 电磁噪声小的电路拓扑 ,如在同等条件下双管正激拓扑比单管正激拓扑产生电磁噪声要小 ,全桥电路比半桥电路产生电磁噪声 要小。

如图所示增加吸收电路后开关管上的电流、电压波形与没有吸收回路时的波形比较。

半桥逆变电路

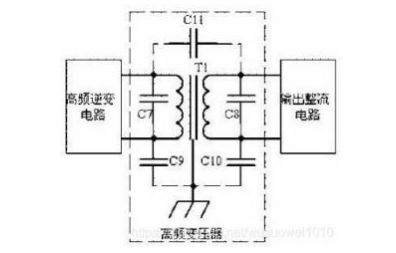

3.高频变压器的电磁兼容设计

在高频变压器T1的设计时 ,尽量选用电磁屏蔽性较好的磁芯材料。

如图所示 ,C7、C8为匝间耦合电路 ,C11为绕组间耦合电容 ,在变压器绕制时 ,尽量减小分布电容C11, 以减小变压器原边的 高频干扰耦合到次边绕组 。另外为进一步减小电磁干扰 ,可在原、次边绕组间增加一个屏蔽层 ,屏蔽层良好接地 ,这样变压器 原、次边绕组对屏蔽层间就形成耦合电容C9、C10,高频干扰电流就通过C9、C10流到大地。

由于变压器是一个发热元件 ,较差的散热条件必然导致变压器温度升高 ,从而形成热辐射 ,热辐射是以电磁波形式对外传播, 因此变压器必须有很好的散热条件。

通常将高频变压器封装在一个铝壳盒内 ,铝盒还可安装在铝散热器上 ,并灌注电子硅胶 ,这样变压器即可形成较好的电磁屏 蔽 ,还可保证有较好的散热效果 ,减小电磁辐射。

高频变压器的电磁兼容设计

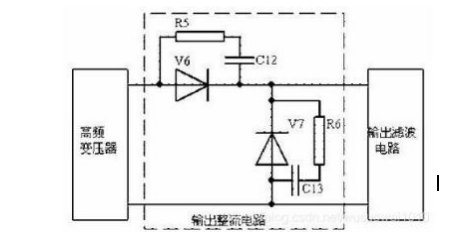

1. 输出整流电路电磁兼容设计

如图所示为输出半波整流电路 ,V6为整流二极管 ,V7为续流二极管 , 由于V6、V7工作于高频开关状态 , 因此输出整流电路的 电磁干扰源主要是V6和V7,R5、C12和R6、C13分别连接成V6、V7的吸收电路 ,用于吸收其开关动作时产生的电压尖峰 ,并 以热的形式在R5、R6上消耗。

减少整流二极管的数量就可减小电磁干扰的能量 , 因此同等条件下 ,采用半波整流电路比采用全波整流和全桥整流产生的电磁 干扰要小。

为减小二极管的电磁干扰 ,必须选用具有软恢复特性的、反向恢复电流小、反向恢复时间短的二极管器件 。从理论上讲 , 肖特 基势垒二极管(SBD)是多数载流子导流 ,不存在少子的存储与复合效应 , 因而也就不会有反向电压尖峰干扰 ,但实际上对于 较高反向工作电压的肖特基二极管 , 随着电子势垒厚度的增加 ,反向恢复电流会增大 ,也会产生电磁噪声 。因此在输出电压较 低的情况下选用肖特基二极管作直流二极管产生的电磁干扰会比选用其它二极管器件要小。

输出整流电路电磁兼容设计

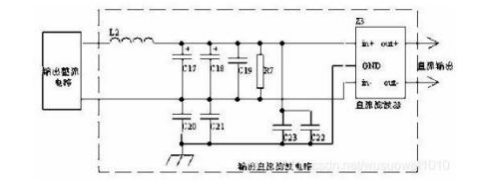

1. 输出直流滤波电路的电磁兼容设计

输出直流滤波电路主要用于切断电磁传导干扰沿导线向输出负载端传播 ,减小电磁干扰在导线周围的电磁辐射。

如图所示 ,L2、C17、C18组成的LC滤波电路 ,能减小输出电流、电压纹波的大小 ,从而减小通过辐射传播的电磁干扰 ,滤波 电容C17、C18尽量采用多个电容并联 ,减小等效串联电阻 ,从而减小纹波电压 ,输出电感L2值尽量大 ,减小输出纹波电流的 大小 ,另外电感L2最好使用不开气隙的闭环磁芯 ,最好不是饱和电感 。在设计时 ,我们要记住 ,导线上有电流、电压的变

化 ,在导线周围就有变化的电磁场 , 电磁场就会沿空间传播形成电磁辐射。

C19用于滤除导线上的共模干扰 ,尽量选用低感电容 ,且接线要短 ,C20、C21、C22、C23用于滤除输出线上的差模干扰 ,宜 选用低感的三端电容 ,且接地线要短 ,接地可靠。

Z3为直流EMI滤波器 ,根据情况使用或不使用 ,是采用单级还是多级滤波器 ,但要求Z3直接安装在金属机箱上 ,最好滤波器输 入、输出线能屏蔽隔离。

输出整流电路电磁兼容设计

1. 接触器、继电器等其它开关器件电磁兼容设计

继电器、接触器、风机等在掉电后 ,其线圈将产生较大的电压尖峰 ,从而产生电磁干扰 ,为此在直流线圈两端反并联一个二极 管或RC吸收电路 ,在交流线圈两端并联一个压敏电阻用于吸收线圈掉电后产生的电压尖峰 。同时要注意如果接触器线圈电源 与辅助电源的输入电源为同一个电源 ,之间最好通过一个EMI滤波器 。继电器触头动作时也将产生电磁干扰 , 因此要在触头两 端增加RC吸收回路。

1. 开关电源箱体结构的电磁兼容设计

材料选择:没有“磁绝缘”材料 , 电磁屏蔽是利用“磁短路”的原理 ,来切断电磁干扰在设备内部与外界空气中的传播路径 。在进 行开关电源的箱体结构设计时 ,要充分考虑对电磁干扰的屏蔽效能 ,对于屏蔽材料的选择原则是 , 当干扰电磁场的频率较高

时 ,选用高电导率的金属材料 ,屏蔽效果较好; 当干扰电磁波的频率较低时 ,要采用高导磁率的金属材料 ,屏蔽效果较好;在 某些场合下 ,如果要求对高频和低频电磁场都具有良好的屏蔽效果时 ,往往采用高电导率和高导磁率的金属材料组成多层屏蔽 体。

孔洞、缝隙、搭接处理方法:采用电磁屏蔽方法无需重新设计电路 ,便可达到很好的电磁兼容效果 。理想的电磁屏蔽体是一个 无缝隙、无孔洞、无透入的导电连续体 ,低阻抗的金属密封体 ,但是一个完全密封的屏蔽体是没有实用价值的 , 因为在开关电 源设备中 ,有输入、输出线过孔、散热通风孔等孔洞 , 以及箱体结构部件之间的搭接缝隙 ,如果不采取措施将会产生电磁泄

漏 ,使箱体的屏蔽效能降低、甚至完全丧失 。因此在开关电源箱体设计时 ,金属板之间的搭接最好采用焊接 ,无法焊接时要使 用电磁密封垫或其它的屏蔽材料 ,箱体上的开孔要小于要屏蔽的电磁波的波长的1/2,否则屏蔽效果将大大降低;对于通风

孔 ,在屏蔽要求不高时可以使用穿孔金属板或金属化丝网 ,在要求既要屏蔽效能高 ,又要通风效果好时选用截至波导管等方

法 ,提高屏蔽体的屏蔽效能 。如果箱体的屏蔽效能仍无法满足要求时 ,可以在箱体上喷涂屏蔽漆 。除了对开关电源整个箱体的 屏蔽之外 ,还可以对电源设备内部的元件、部件等干扰源或敏感设备进行局部屏蔽。

在进行箱体结构设计时 ,针对设备上所有会受到静电放电试验的部分 ,设计出一条低阻抗的电流泄放路径 ,箱体必须有可靠的 接地措施 ,并且要保证接地线的载流能力 , 同时将敏感电路或元件远离这些泄放回路 ,或对其采用电场屏蔽措施 。对于结构件 的表面处理 ,一般主要电镀银、锌、镍、铬、锡 ,这需要从导电性能、电化学反应、成本及电磁兼容性等多方面考虑后做出选 择。

1. 元器件布局与布线中的电磁兼容设计:

对于开关电源设备内部元器件的布局必须整体考虑电磁兼容性的要求 ,设备内部的干扰源会通过辐射和串扰等途径影响其它元 件或部件的工作 ,研究表明 ,在离干扰源一定距离时 ,干扰源的能量将大大衰减 , 因此合理的布局有利于减小电磁干扰的影

响。

EMI输入输出滤波器最好安装在金属机箱的入口处 ,并保证其输入线与输出线电磁环境的屏蔽隔离。

敏感电路或元件要远离发热源。

对于开关电源产品 ,我们一般须遵守以下布线原则:

9.1 主电路输入线与输出线分开走线。

9.2 EMI滤波器输入线与输出线分开走线。

9.3 主电路线与控制信号线分开走线。

9.4 高压脉冲信号线最好分开单独走线。

9.5 分开布线的原则是避免平行走线 ,可以垂直交叉 ,线束之间距离在20mm以上。

9.6 电缆不要贴着金属外壳和散热器走线 ,保证一定距离。

9.7 双绞线、同轴电缆及带状电缆在EMC设计中的使用

双绞线的使用

双绞线、同轴电缆都能有效的抑制电磁干扰 。在脉冲信号传输线路中常使用双绞线 ,控制辅助电源线和传感器信号线最好用双 绞屏蔽线 。因为双绞线两根线之间有很小的回路面积 ,而且双绞线的每两个相邻的回路上感应出的电流具有大小相等、方向相 反 ,产生的磁场相互抵消 ,这样就可以减小因辐射引起的差模干扰 ,不过双绞线绞合的圈数最好为偶数 ,且每单位波长所绞合 的圈数愈多 ,消除耦合的效果愈好 。使用时注意双绞线和同轴电缆两端不能同时接地 , 只能单端接地 ,而对屏蔽线 ,屏蔽层两 端接地能既能屏蔽电场还能屏蔽磁场 ,单端接地只能屏蔽电场 。使用同轴电缆时还要注意 ,其屏蔽层必须完全包覆信号线接

地 , 即接头与电缆屏蔽层必须3600搭接 ,才能有效屏蔽电磁场 ,如图所示 ,信号线裸露部分仍可以与外界形成互容耦合 , 降低 屏蔽效能。

带状电缆适合于短距离的信号传输 ,我们知道为了降低差模信号的电磁辐射 ,必须减小信号线和信号回流线所形成的回路面 积 , 因此在设计带状电缆布局时 ,最好将信号线与接地线间隔排列 。如图所示 ,其中S为信号线 ,G为信号地线。

信号线与接地线间隔排列

10.元器件的选择

热传播的方式有传导、对流和辐射 ,热辐射是以电磁波的形式向空中传播的 ,热传导也会向周围其它元件传导热量 ,这些都会 影响其它元器件或电路的正常工作 , 因此从元器件热设计方面考虑要尽量留有较大余量 , 以降低元器件的温升及器件表面的温 度 , 除元器件对温升有特殊要求外 ,一般开关电源要求内部元件温度小于90℃, 内部环境温度不超过65℃, 以减小热辐射干 扰。

对数字集成电路 ,从电磁兼容性角度看应多选用高噪声容限的CMOS器件代替低噪声容限的TTL器件。

尽量使用低速、窄带元件和电路。

选用分布电感较小的SMP元件 ,选用高频特性好、等效串联电感低的陶瓷介质电容器、高频无感电容器、三端电容器和穿心电 容器等作滤波电容。

11.控制电路及PCB的电磁兼容设计

信号地是指信号电流流回信号源的一条低阻抗路径 。在设计中往往由于接地方法不恰当而产生地环路干扰和公共阻抗耦合干 扰 。因此要合理选用接地方式 ,接地的方式有单点接地、多点接地和混合接地。

地环路干扰:常发生在通过较长电缆连接 ,地相距较远的设备之间 。原因是由于地环路电流的存在 ,使两个设备的地电位不 同 。通常用光电耦合器或隔离变压器进行“地”隔离 ,消除地环路干扰 。由于隔离变压器绕组之间寄生电容较大 , 即使采取屏蔽 措施的隔离变压器通常也只用于1MHZ以下的信号隔离 ,超过1MHZ时多采用光电耦合器隔离。

公共阻抗耦合: 当两个电路的地电流流过一个公共阻抗时 ,就会发生公共阻抗耦合 。由于地线是信号回流线 ,一个电路的工作 状态必然会影响地线电压 , 当两个电路共用一段地线时 ,地线的电压就会同时受到两个电路工作状态的影响。

可见无论是地环路干扰还是公共阻抗耦合问题都是由于地线阻抗引起的 , 因此在设计时一定要考虑尽量降低地线阻抗与感抗。

如何减小控制电源噪声: 电源线上有电流突变 ,就会产生噪声电压 。在靠近芯片的位置增加解耦电容 ,能有效减小噪声 。如果 是高频电流负载 ,则采用多个同容量的高频电容和无感电容并联能获得更好的效果 。注意电容容量并非越大越好 ,主要根据其 谐振频率、提供脉冲电流频率来选择。

印制板合理的布置地线将能有效的减小印制板的辐射以及提高其抗辐射干扰能力 ,请注意

l 布置地线网络:在双面板的两面布置最多的平行地线。

l 对于一些关键信号(如脉冲信号和对外界较敏感的电平信号) 的地线的布置必须尽量缩小引线长度 ,减小信号的回流面积。 如果是双面板 ,地线和信号线可以在印制板两面并联平行走线。

l 若是多层线路板 ,且既有数字地又有模拟地 ,则数字地和模拟地必须布置在同一层 ,减小它们之间的耦合干扰。 l 在实际电路中常发生公共阻抗耦合 , 因此要根据实际情况选择正确的接地方式。

12.其它方法

12.1.IGBT,MOSFET等开关元件的驱动脉冲信号增加一个-5V~- 10V的负电平 ,提高驱动信号的抗干扰能力 。或驱动信号采用 光纤传输技术 ,光纤适宜于远距离传输 ,具有抗干扰能力强的特点。

12.2.通过软件的编程技术 ,提高开关电源的抗干扰能力 ,为了防止电平信号中的毛刺 , 引起软件的误判断及误动作 ,可以通过 多次采样等数字滤波方法来滤除干扰信号。

五 结语

本文详细分析了隔离式DC/DC变换器存在的电磁干扰源及其产生机理 ,并详细介绍了针对其主电路和控制电路的电磁兼容设计 方法 ,这些方法对其它电子产品的电磁兼容设计具有一定的指导作用。

审核编辑:黄飞

-

隔离式DC/DC变换器的电磁兼容设计2009-10-12 0

-

降压式DC-DC变换器资料下载2009-10-31 0

-

隔离式DC/DC变换器的电磁兼容设计(ZT)2012-01-11 0

-

选择最佳DC/DC变换器的要点及途径2014-06-05 0

-

升压式DC_DC变换器LM2623(资料下载)2017-10-26 0

-

分享【基于磁隔离双向传输的多功能DC/DC变换器设计】2020-08-07 0

-

怎么解决FCEV用大功率DC/DC变换器电磁干扰问题?2021-05-17 0

-

最佳的开关式DC/DC变换器2021-11-16 0

-

DC-DC变换器的基本电路2021-11-17 0

-

DC-DC变换器的应用2021-11-17 0

-

电池驱动系统的DC-DC变换器选择2023-03-03 0

-

一族新颖的桥式混合DC/DC变换器2009-06-20 862

-

隔离式DC/DC变换器的电磁兼容设计2009-10-17 736

全部0条评论

快来发表一下你的评论吧 !