资料下载

在可穿戴式设计中选择外围设备和集成存储器

在可穿戴式设计中选择外围设备和集成存储器

新一代可穿戴技术正在启用高度集成的片上系统(SoC)设计。最新的32位微控制器核心从ARM和MIPS提供高性能的支持,如Android Wear新的操作系统,并加入了广泛的外设,以支持新的显示器,交互式接口和传感器应用。

移动到32位内核允许高级开发工具不仅用于用户应用程序,还用于整个设计的管理,特别是外围设备的电源管理。能够实现复杂的算法,以优化功耗是至关重要的,以获得最佳的电池寿命,这是紧密耦合的外设在系统芯片上实现的可穿戴式设计设备。

The choice of the processor core architecture is often down to the experience of the system architect and the design team, as well as strategic corporate relationships. There are many designers adept at developing on both the ARM and MIPS platforms, using high level C development tools and the peripheral management tools that come with each of the different silicon suppliers.

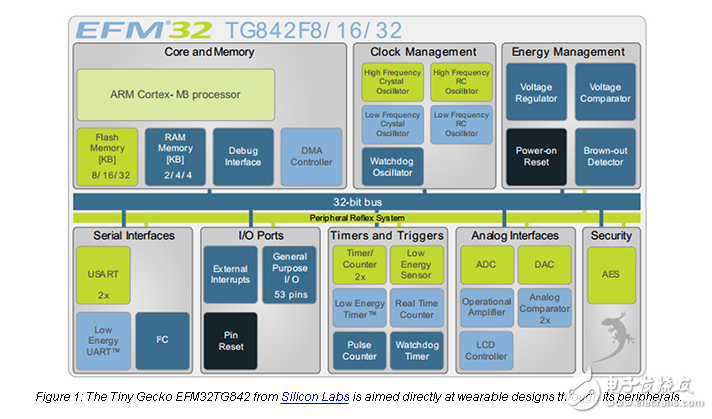

Devices such as Silicon Labs‘ Tiny Gecko EFM32TG842 with a central ARM Cortex-M3 processor core (shown in Figure 1) are aimed directly at wearable designs with a small size and low power consumption but also a range of peripherals optimized for such applications. Freescale Semiconductor also has a range of system-on-chip devices based on the ARM Cortex-M0+ devices in its KL16 family that are part of its WaRP wearable development platform.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章