资料下载

摩尔定律工艺节点的形成介绍及导体工艺节点的演进分析

摩尔定律下的工艺节点的形成

1958年,美国德州仪器公司的工程师杰克·基尔比制成了世界上第一片集成电路,1962年,德州仪器公司建成世界上第一条商业化集成电路生产线。此后,在市场需求的驱动下,集成电路发展成为一个庞大的产业,从小规模集成电路(SSI)到中规模集成电路(MSI)、再到大规模集成电路(LSI),一直到现在的超大规模集成电路(VLSI)。集成度被看作是描述集成电路工艺先进程度的一个重要指标,通常用晶体管数目来表示集成度高低,一个芯片里含有的晶体管数目越多,芯片的功能也就越强。因此,集成电路的规模反映了集成电路的先进程度。

集成度的提高,不仅意味着单个晶体管的尺寸缩小了,同时也意味着采用了更加先进的制造工艺,因为晶体管尺寸与制造工艺之间有着密切的联系。可以说,集成电路技术的发展过程,就是把晶体管尺寸做得越来越小的过程。九十年代的大规模集成电路普遍采用的是微米级工艺,笔者在上世纪90年代初做设计时就是采用5微米和3微米标准单元库,这也是那个年代的主流工艺(晶圆尺寸是3英寸和4英寸)。二十多年过去了,现在已经发展到纳米级工艺了,中芯国际去年实现量产的28纳米工艺,比起3微米工艺,尺寸缩小了100多倍。

这些工艺演进的背后,是更多金钱的投入。因为更小的尺寸意味着对设计和制造设备以及芯片材料等都有更为苛刻的要求,为了克服技术门槛,芯片企业每年需要投入数亿、数十亿美元的研发经费,不知有多少世界一流的科学家和工程师都参与了这一耗资巨大的芯片微缩化工程。

那么5微米、3微米、以及90纳米、28纳米等等这些“节点”是怎样形成的呢?可以说这是描述摩尔定律进程的一个指标。摩尔定律说,半导体芯片每一年半(后来改为两年),其集成度翻一番,并伴随着性能的增长和成本的下降。怎样描述这个集成度呢?这就有了工艺“节点”的说法。即工艺节点数值越小,表征芯片的集成度就越高。这些数值也被《国际半导体技术蓝图(ITRS)》用来划分半导体工艺的阶段(也称工艺代),或描述芯片的先进性。

这里有必要解释这些数值表示的是什么尺寸。例如28nm工艺,这里的28nm是指晶体管栅极的最小线宽(栅宽)。实际设计中除了栅极,其他的设计尺寸一般都大于工艺节点的尺寸,例如晶体管之间的金属连线宽度、有源区宽度等。

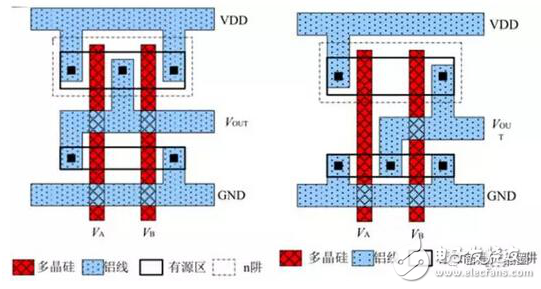

▲ 图一 与非门、或门的版图

图一是个例子。在这个与非门和或非门的版图里,白的是衬底层,红的是多晶硅层,蓝的是金属层。这其中只有红的多晶硅栅极的最小线宽是可以达到28nm的,其他一切尺寸都是要大于28nm。具体各层线宽的最小值需要看该工艺的设计规则(Design Rull)。

为什么用栅极线宽而不是其他的线宽来表征工艺节点,这是因为栅极宽度一般是整个设计中最重要的参数。在CMOS电路中,MOS晶体管最主要的功能就是通过栅极控制源漏之间的电流。这个电流受很多因素影响,例如晶体管迁移率、绝缘层电容,还有各种效应等,这些都与半导体工艺有关,工艺定了设计很难改变。一般情况下唯一可以设计的参数就是沟道宽长比,沟道宽长比就是晶体管栅极的长宽比(长沟器件可以直接近似,短沟器件要加修正项)。也就是说在电压一样的情况下,栅极越宽,沟道就越长,源漏电流就越小。

所以在设计中,沟道越短,意味着晶体管的尺寸越小,单位面积可以存放的晶体管数量就越多,芯片集成度就越高;换一种说法是设计出来的芯片面积就越小,芯片的价格就越便宜。当然这是在只考虑生产成本,不考虑NRE费用的前提下。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章