资料下载

基于i.MX286应用处理器勘误表

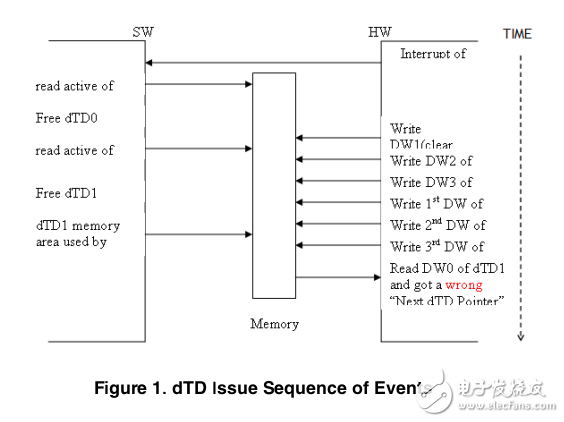

Currently, software checks the active bit in dTD to see whether it is finished. If the Active bit is 0,

then software frees the allocated memory for the dTD.

The hardware sequence after all data of a dTD is transferred is as follows:

1. Update the dTD. This includes an AHB write access of three DWords. The active bit is cleared

in the first DW write.

2. Update the qHead (this includes an AHB write access of three DWords)。

3. Read the dTD again to check if software added a new dTD (this is a SINGLE AHB read)。 At

the same time, send out an interrupt if needed.

After step 1, if software finds the Active bit is cleared, then the dTD memory space is freed and

may be allocated for another thread’s use. In step 3, hardware may get a wrong dTD.

This issue does not occur if some delay is added before freeing the dTD memory space.

This issue only occurs in USB INCR8 mode, because steps 1 and 2 have 6 SINGLE AHB transfers

in INC8 mode, but only two burst AHB transfers in INCR mode.

This issue only occurs when the dTD list is used; because if only one dTD is used, the software

only checks the Active bit after an interrupt is received (step 3)。 However, when the dTD list is

used, the software may check the entire list after the interrupt for the first dTD is received, when

the hardware has just finished the transfer of the second dTD.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章