资料下载

高速数据存储管理设计和基于FPGA高速图像数据的存储及显示设计

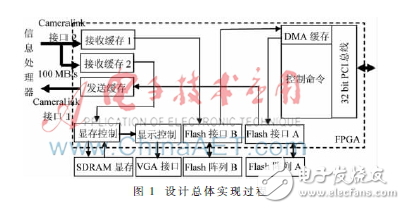

设计了一种基于FPGA控制Nand Flash阵列实现高速流水线式存储的方案。设计利用FPGA作为主控制器,通过CameraLink输入通信接口将图像数据经过一/二级缓存写入Flash存储阵列中,并采用DMA传输技术将存储后的图像数据上传至计算机硬盘中作进一步处理;同时,利用SDRAM显存实时刷新数据,FPGA构造相应的VGA信号,最终实现100 MB/s图像数据的实时显示。

随着数据存储设备被广泛应用于航空航天系统、医疗卫生、工业自动化等各行各业,对于图像设备采集的控制及实时大容量高速存储要求也越来越高。本文以Micron Flash为存储介质,通过FPGA控制实现Camera Link高速接口通信,传输速率可达到100 MB/s,并设计高速数据的流水线式存储方式,实现大容量高速图像存储与实时显示。

1 总体设计

设计的实现过程如图1所示,上位机通过PCI总线下发图像数据并将数据保存在Flash存储阵列A中;上位机指令下发后,FPGA控制Flash A读出存储的数据并通过CameraLink1输出接口发送至信息处理器;待信息处理器处理完数据,再通过CameraLink输入接口2将数据写入到SDRAM显存和Flash存储阵列B中,使能VGA显示后,显示控制循环读取SDRAM中的图像数据进行显示;最后,上位机通过DMA传输将Flash阵列B中保存的数据快速上传至上位机中以作后续处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

gsr668103

2017-10-25

0 回复 举报学习了,谢谢楼组分享 收起回复

gsr668103

2017-10-25

0 回复 举报学习了,谢谢楼组分享 收起回复

- 相关下载

- 相关文章