资料下载

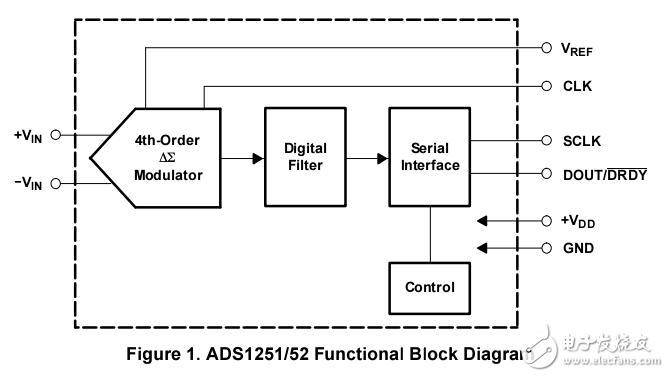

ADS125152到MSP430的接口温度传感器

The foundation of the ADS1251/52 is the sigma-delta modulator. Although detailed theory of this class of

data converter is beyond the scope of this application report, the fundamental operation of this converter is

discussed. Figure 2 shows a first-order sigma-delta modulator, which operates as follows.

The modulator’s function is to reduce the error between the input signal and the previous output to zero.

Assuming a dc input at A, this dc value is applied to a summing point and added to the value from the

DAC, E. If the output from the summing junction is positive, the integrator output continues to ramp up

until it trips the comparator. The comparator then signals to the DAC that the input has passed its upper

threshold. In turn, the DAC then begins to reduce the effective signal at B, and the integrator begins to

ramp down. The integrator continues to ramp down until it trips the comparator again. The comparator

then signals to the DAC that the input has passed its lower threshold. In turn, the DAC then begins to

increase the effective signal at B, and the integrator begins to ramp up again.

Because the comparator is latched, this action performs the quantization in time of the analog signal. The

quantization in amplitude is accomplished through the density of the pulses originating from the

comparator. If the input signal is close to full scale, more 1 pulses occur than 0 pulses in the bit stream

from the comparator. Conversely, if the input-signal is close to negative full scale, more 0 pulses occur

than 1 pulses in the bit stream from the comparator. Signals near midscale have equal numbers of 1 and

0 pulses. Figure 3 shows this graphically.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章