资料下载

MSP430x5xx MSP430x6xx Family User's Guide

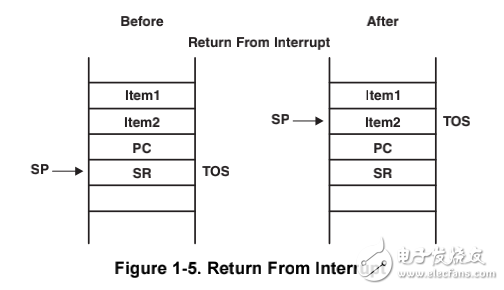

The low-power modes LPM0 through LPM4 are configured with the CPUOFF, OSCOFF, SCG0, andSCG1 bits in the SR. The advantage of including the CPUOFF, OSCOFF, SCG0, and SCG1 mode-controlbits in the SR is that the present operating mode is saved onto the stack during an interrupt serviceroutine. Program flow returns to the previous operating mode if the saved SR value is not altered duringthe interrupt service routine. Program flow can be returned to a different operating mode by manipulatingthe saved SR value on the stack inside of the interrupt service routine. When setting any of themode-control bits, the selected operating mode takes effect immediately. Peripherals operating with anydisabled clock are disabled until the clock becomes active. Peripherals may also be disabled with their

individual control register settings. All I/O port pins and RAM/registers are unchanged. Wakeup from LPM0through LPM4 is possible through all enabled interrupts.When LPMx.5 (LPM3.5 or LPM4.5) is entered, the voltage regulator of the Power Management Module(PMM) is disabled. All RAM and register contents are lost. Although the I/O register contents are lost, theI/O pin states are locked upon LPMx.5 entry. See the Digital I/O chapter for further details. Wakeup fromLPM4.5 is possible via a power sequence, a RST event, or from specific I/O. Wakeup from LPM3.5 ispossible via a power sequence, a RST event, RTC event, or from specific I/

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章