资料下载

×

DSP系统通用设计模式及其实现

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-20

引言

目前,随着视频处理领域的不断深入发展,作为其实现的主要平台——DSP系统的设计成为了决定视频处理算法是否能高速实时运行的首要因素。

一个优秀的DSP系统框架应该至少具有功能的高效实施性和良好的软硬件扩展性。本文介绍的这种基于视频处理的DSP系统的框架正是以传统的数字信号处理方式为基础,以高效性和扩展性为目标,并且能够适应大多数的器件而提出的在硬件上和在软件上的解决方案。

可通用设计模式的思路

硬件结构

传统的数字信号处理过程是由“ADC + DSP + DAC”这种模式构成的,其中并未具体的明确指出存储器的如何使用以及ADC、DSP和DAC之间的数字逻辑电路关系如何,而这两点正是实现高效实时系统的关键所在。

以视频处理为背景,基于可通用设计模式的思路从硬件功能上将DSP系统按图1中所示的模块框图设计。从图中可以看到整个DSP系统被分为六大模块:DSP模块、ADC模块、DAC模块、存储器模块、数字逻辑电路模块和其它模块。其中,数字逻辑电路模块起到了模块间相互通信的中间“桥”作用,通常选用具有足够的可编程引脚和内部逻辑单元的CPLD或FPGA加上适当数目的开关器件来实现;而存储器模块则由针对DSP模块、ADC模块和DAC模块的三个独立且结构相同的子模块组成。

由于各存储器子模块间的地址总线、数据总线和控制总线的相互独立,通过数字逻辑电路模块可以使ADC、DSP和DAC三个模块在同一时刻拥有各自独立的存储空间从而为三者的并行无阻碍运行提供了有效的硬件保证。如图2中所示,三个存储器子模块处于循环式的流水线工作状态,它们在系统中的地位等价;其中每个存储器子模块一般都以整帧图像为存储单位,故可简称为帧存。整个系统处于ADC、DSP和DAC三个模块同步并行的工作方式,即DSP处理当前帧图像的同时ADC正采集下一帧图像而DAC正传送上一帧图像给显示设备,这样DSP只负责图像的处理过程而不涉及图像在存储空间中的简单搬移。

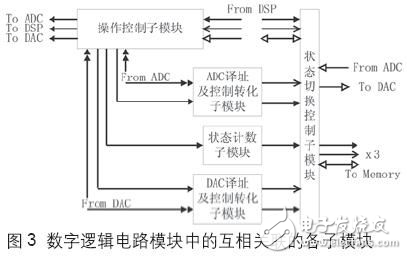

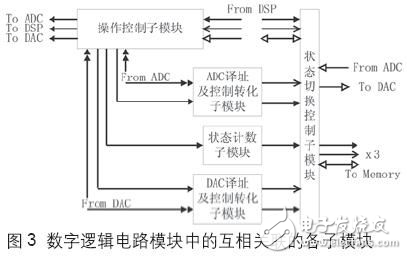

相应的数字逻辑电路模块按图3中所示的互相关联的各子模块来设计。其中,操作控制子模块用于实现DSP对ADC及DAC的控制(复位或下电ADC及DAC、选择标准I2C或模拟I2C进行配置、同步三者的并行等)与DSP外部中断的使能,并控制图3中其它的子模块;状态计数子模块用于产生四类状态:上电初始态和三类工作态;ADC或DAC译址及控制转化子模块用于产生ADC或DAC控制相应存储空间的逻辑;状态切换控制子模块则通过接收图3中其它子模块的信息来最终实现存储空间与ADC、DSP及DAC的相互对应。

当系统设计中不要求使用DAC或ADC时,图4中示出了图1中模块互连部分与图2的简化;由此可以看出以上基于可通用设计模式的DSP系统框架简化为了具有以乒乓式存取的双存储器子模块的情况,故基于乒乓式存取的数据系统是其特例。此外,该框架可以实现多路ADC及多路DAC的并行工作,通常选用相应数目的SDRAM作为存储器子模块来配合使用。

目前,随着视频处理领域的不断深入发展,作为其实现的主要平台——DSP系统的设计成为了决定视频处理算法是否能高速实时运行的首要因素。

一个优秀的DSP系统框架应该至少具有功能的高效实施性和良好的软硬件扩展性。本文介绍的这种基于视频处理的DSP系统的框架正是以传统的数字信号处理方式为基础,以高效性和扩展性为目标,并且能够适应大多数的器件而提出的在硬件上和在软件上的解决方案。

可通用设计模式的思路

硬件结构

传统的数字信号处理过程是由“ADC + DSP + DAC”这种模式构成的,其中并未具体的明确指出存储器的如何使用以及ADC、DSP和DAC之间的数字逻辑电路关系如何,而这两点正是实现高效实时系统的关键所在。

以视频处理为背景,基于可通用设计模式的思路从硬件功能上将DSP系统按图1中所示的模块框图设计。从图中可以看到整个DSP系统被分为六大模块:DSP模块、ADC模块、DAC模块、存储器模块、数字逻辑电路模块和其它模块。其中,数字逻辑电路模块起到了模块间相互通信的中间“桥”作用,通常选用具有足够的可编程引脚和内部逻辑单元的CPLD或FPGA加上适当数目的开关器件来实现;而存储器模块则由针对DSP模块、ADC模块和DAC模块的三个独立且结构相同的子模块组成。

由于各存储器子模块间的地址总线、数据总线和控制总线的相互独立,通过数字逻辑电路模块可以使ADC、DSP和DAC三个模块在同一时刻拥有各自独立的存储空间从而为三者的并行无阻碍运行提供了有效的硬件保证。如图2中所示,三个存储器子模块处于循环式的流水线工作状态,它们在系统中的地位等价;其中每个存储器子模块一般都以整帧图像为存储单位,故可简称为帧存。整个系统处于ADC、DSP和DAC三个模块同步并行的工作方式,即DSP处理当前帧图像的同时ADC正采集下一帧图像而DAC正传送上一帧图像给显示设备,这样DSP只负责图像的处理过程而不涉及图像在存储空间中的简单搬移。

相应的数字逻辑电路模块按图3中所示的互相关联的各子模块来设计。其中,操作控制子模块用于实现DSP对ADC及DAC的控制(复位或下电ADC及DAC、选择标准I2C或模拟I2C进行配置、同步三者的并行等)与DSP外部中断的使能,并控制图3中其它的子模块;状态计数子模块用于产生四类状态:上电初始态和三类工作态;ADC或DAC译址及控制转化子模块用于产生ADC或DAC控制相应存储空间的逻辑;状态切换控制子模块则通过接收图3中其它子模块的信息来最终实现存储空间与ADC、DSP及DAC的相互对应。

当系统设计中不要求使用DAC或ADC时,图4中示出了图1中模块互连部分与图2的简化;由此可以看出以上基于可通用设计模式的DSP系统框架简化为了具有以乒乓式存取的双存储器子模块的情况,故基于乒乓式存取的数据系统是其特例。此外,该框架可以实现多路ADC及多路DAC的并行工作,通常选用相应数目的SDRAM作为存储器子模块来配合使用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章