资料下载

1.2A降压稳压器和两个300毫安LDO微系统ADP5040数据表

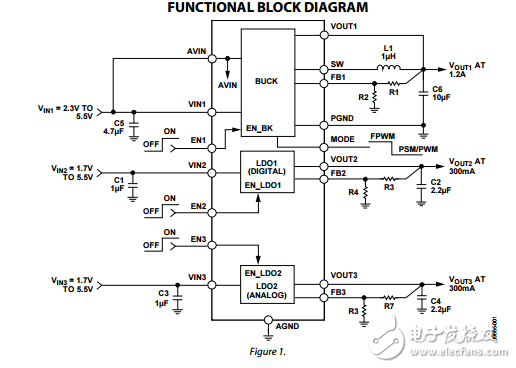

The ADP5040 combines one high performance buck regulator and two low dropout regulators (LDO) in a small 20-lead LFCSP to meet demanding performance and board space requirements. The high switching frequency of the buck regulator enables the use of tiny multilayer external components and minimizes board space. When the MODE pin is set to logic high, the buck regulator operates in forced pulse width modulation (PWM) mode. When the MODE pin is set to logic low, the buck regulator operates in PWM mode when the load is around the nominal value. When the load current falls below a predefined threshold the regulator operates in power save mode (PSM) improving the light-load efficiency. The low quiescent current, low dropout voltage, and wide input voltage range of the ADP5040 LDOs extend the battery life of portable devices. The ADP5040 LDOs maintain a power supply rejection greater than 60 dB for frequencies as high as 10 kHz while operating with a low headroom voltage. Each regulator in the ADP5040 is activated by a high level on the respective enable pin. The output voltages of the regulators are programmed though external resistor dividers to address a variety of applications.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章