资料下载

×

达芬奇DMSoC硬件部分及Linux OS的启动过程

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-06

达芬奇(DaVinci)数字媒体技术平台TMS320DM6446/3采用了ARM+DSP双核的架构,本文从芯片的硬件结构入手介绍达芬奇DMSoC硬件部分及Linux OS的启动过程。

达芬奇DMSoC硬件概述

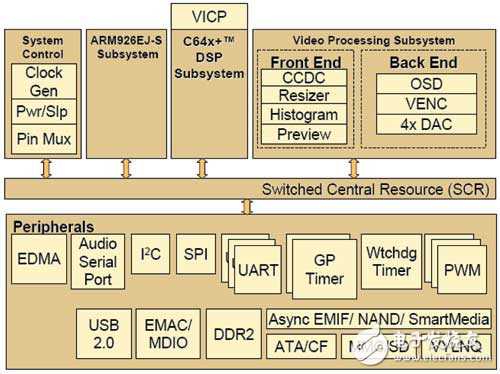

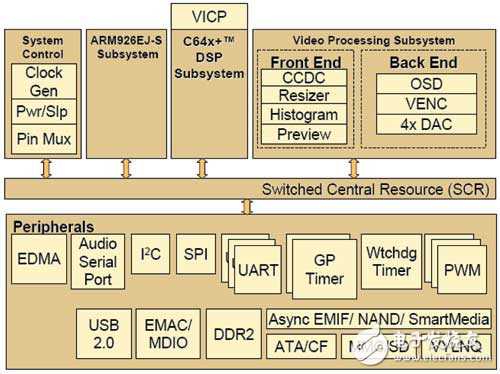

如图1所示,达芬奇数字媒体片上系统(DMSoC)提供:两个内核(ARM+DSP);视频处理子系统(VPSS);多种Boot模式(NOR Flash/NAND Flash/UART0 Boot Mode);两个电源域;多个时钟树;多个引脚独立或复用的外设。

图1 DM6446功能结构框图

● ARM-DSP集成

对于双核的达芬奇架构,大家最关心的就是两个核之间的资源分配、通信方式及如何高效地实现资源共享各尽其能。ARM独享(DSP不可用)的外设有:UART0/1/2,I2C,看门狗定时器,PWM0/1/2,ARM中断控制器,USB2.0,ATA/CF,SPI,GPIO,VPSS,EMAC/MDIO,EMIFA CONTROL,VLYNQ,MMC/SD。DSP独享(ARM不可用)的外设有:DSP中断控制器,VICP。ARM和DSP共享的外设有:EDMA,Timer0/1,Power & Sleep Controller,ASP和EMIFA Data。

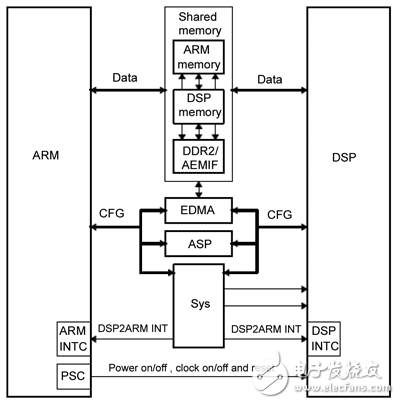

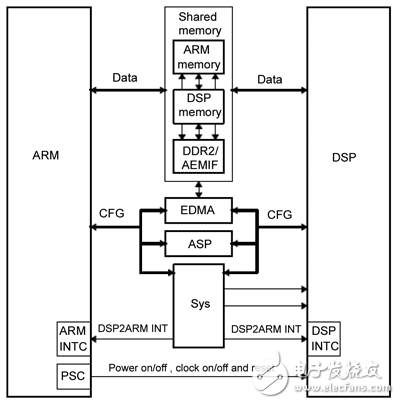

图2 ARM-DSP集成结构

如图2所示,可以很清楚地看到ARM可以访问DSP片内存储器(L2RAM和L1P/D);DSP可以访问ARM片内存储器;ARM和DSP共享DDR2和AEMIF。因此,通常情况下ARM只需传递需要处理的数据地址指针给DSP,而无须大块的数据搬移。ARM和DSP之间的通信可以通过相互中断实现。ARM可以中断DSP(通过4个通用中断和1个不可屏蔽中断);DSP可以通过2个通用中断来中断ARM。ARM控制DSP的电源、时钟、复位和引导。

达芬奇DMSoC硬件概述

如图1所示,达芬奇数字媒体片上系统(DMSoC)提供:两个内核(ARM+DSP);视频处理子系统(VPSS);多种Boot模式(NOR Flash/NAND Flash/UART0 Boot Mode);两个电源域;多个时钟树;多个引脚独立或复用的外设。

图1 DM6446功能结构框图

● ARM-DSP集成

对于双核的达芬奇架构,大家最关心的就是两个核之间的资源分配、通信方式及如何高效地实现资源共享各尽其能。ARM独享(DSP不可用)的外设有:UART0/1/2,I2C,看门狗定时器,PWM0/1/2,ARM中断控制器,USB2.0,ATA/CF,SPI,GPIO,VPSS,EMAC/MDIO,EMIFA CONTROL,VLYNQ,MMC/SD。DSP独享(ARM不可用)的外设有:DSP中断控制器,VICP。ARM和DSP共享的外设有:EDMA,Timer0/1,Power & Sleep Controller,ASP和EMIFA Data。

图2 ARM-DSP集成结构

如图2所示,可以很清楚地看到ARM可以访问DSP片内存储器(L2RAM和L1P/D);DSP可以访问ARM片内存储器;ARM和DSP共享DDR2和AEMIF。因此,通常情况下ARM只需传递需要处理的数据地址指针给DSP,而无须大块的数据搬移。ARM和DSP之间的通信可以通过相互中断实现。ARM可以中断DSP(通过4个通用中断和1个不可屏蔽中断);DSP可以通过2个通用中断来中断ARM。ARM控制DSP的电源、时钟、复位和引导。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章