资料下载

×

基于SOPC技术的嵌入式千兆以太网接口设计

消耗积分:0 |

格式:rar |

大小:0.2 MB |

2017-11-07

运用 SOPC技术流程和嵌入式系统完成了基 于 FPGA千兆速率接 口设计 ,工程主要分为硬件环境的构建和软件执行环境的配置。设计实现 了将以太网的传输速率提 高到 1O00M模式,具有一定的工程实际参考价值 。

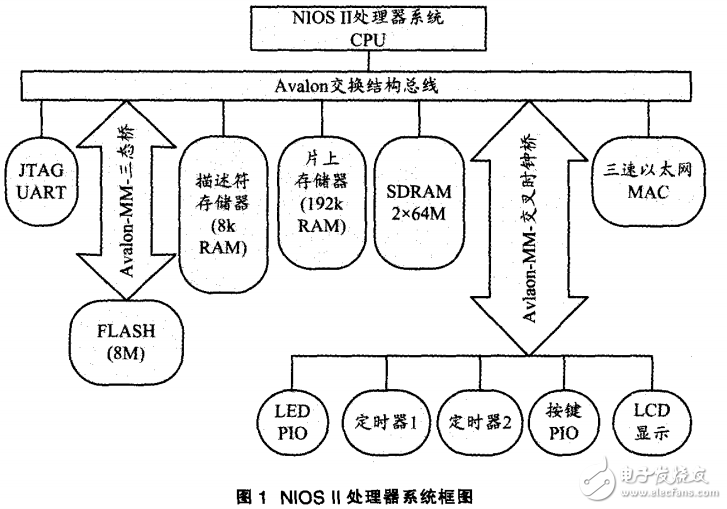

工 程 采用 Ahera的 开发 套板 DE2—115.主要是以CycloneIV EEP4CE115F29C7型 号 的 FPGA芯片为主体 .采用 NIOSII处理器软核配置工程 .用 QuartusII 10.1SP1环境中的 SOPC Builder工具 进 行 硬 件 搭 建 .构成 以 NIOSII处 理 器为 中心 .通过 AVALON总 线将三速以太 网核 、存储器 sDRAM和 FLASH等外设连接在一起的硬件系统环境 。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章