资料下载

×

基于FPGA的多功能数字钟设计原理

消耗积分:0 |

格式:rar |

大小:0.2 MB |

2017-11-30

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是一种可编程使用的信号处理器件。通过改变配置信息,用户可对其功能进行定义,以满足设计需求。通过开发,FPGA 能够实现任何 数字器件的功能。与传统数字电路相比,FPGA 具有可编程、高集成度、高可靠性和高速等优点。

世界时钟模块的工作原理及设计实现

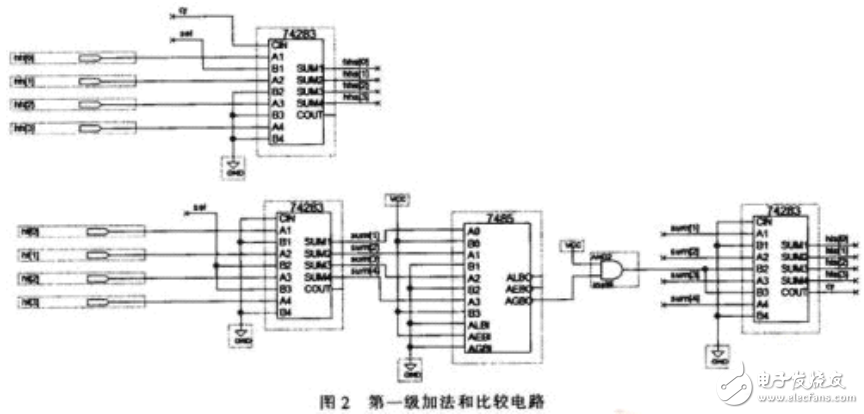

本设计中加入了世界时钟模块,能够将北京时间快速转换为格林威治标准时。北京位于东八区,格林威治 位于本初子午线附近,北京时间比格林威治标准时快8小时,要完成时间转换,需要将北京时间减去8小时,在24进制中相当于加16小时。基于此设计加法和比 较电路。在时计数器输出信号的基础上,利用74283四位全加器将时低位加6(01102),时高位加1(0001 2)。由于74283四位全加器为16进制,而时较器判断计算结果是否大于9,若结果大于9,则需要在此基础上继续加6,将结果修正为十进制,过程中产生 的进位信号作为时高位的 CIN 信号;若结果小于9,则可直接输出。第一级加法和比较电路如图2所示。完成时低位加6,时高位加1的变换后,需要判断变换后 的时间是否大于24.若大于24,则需要减24;若小于24,则可直接输出。世界时间转换流程图如图3所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章