资料下载

×

电路设计时钟高速数据转换器正确选择使用的小技巧资料概述

消耗积分:0 |

格式:rar |

大小:0.30 MB |

2018-05-16

在电路设计中,涉及到使用高性能、高速模数转换器(ADC),如ADS5500,主要的一个注意事项是时钟方案。关于要使用的时钟类型(正弦或正方形)、电压电平或抖动的问题是常见的。本文的目的是解释支持电路设计者做出正确选择的一般理论。

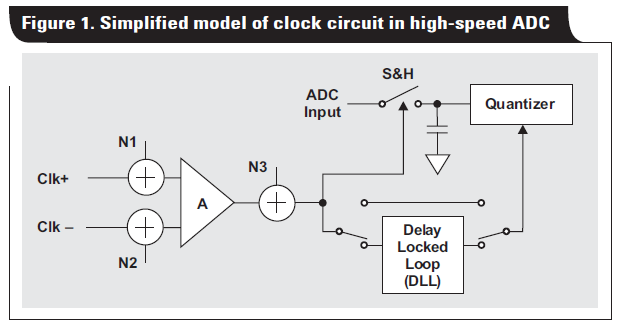

图1显示了高速ADC内部的时钟电路的简化模型,如ADS5500。虽然并非所有的ADC在它们的时钟分布中都有完全相同的内部块,但是这个图可以被修改以适合您的特定ADC。从现在起,作为ADC销售的电路大多包括前采样和保持(S&H),为了这篇文章的目的,我们将区分它们。将输入信号的瞬时模拟快照的电路称为S&H;ADC本身将S&H所保持的模拟值转换成量化的数字输出,将被称为量化器。分析内部时钟的哪些参数对于这两个电路是重要的,将有助于我们理解外部时钟设计中的主要注意事项。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章