锁相环的研究和频率合成

电子实验

描述

锁相环的研究和频率合成

一、实验目的:

1. 振荡器(VCO)的V—f 特性的研究

2. 对称波锁相环基本特性的研究

3. 利用锁相环实现频率合成

二、锁相环原理:

锁相环(Phase Lock Loop )是一个自动相位控制系统,框图3-1 描述了一个基本锁

相系统的主要组成部分,其中包括相位比较器( Phase Detector)、电压控制振荡器( Voltage

Controlled Osillator)、低通滤波器(Low Past Filter )。

这个系统的传递函数H(S)可以用下列方程描述:

100KHZ晶体

100KHZ晶体

所以,框图3-1 表示的系统是一个典型的全反馈系统,

G(S)为系统的开环传递函数,它由Ko、Kd、F(S)来确定。

本实验中用一片74LS221 双单稳态电路组成VCO 振荡器,原理如图3-2,改变A 点电

压就能改变振荡频率,一般A 点电压位1.1 伏以上就开始振荡,输出频率还与R1、R2、R3

以及C1、C2 值有关。通过实验测出f—Vc 关系曲线如图3-2 所示,并可看出Δf/ΔV 在不同

控制电平下,并不全部一样,在低电平处Δf/ΔV 值比较大。而高电平处却比较小,这就决

定了最佳控制点的选择(线性部分)。

2、相位比较器(PD)

相位比较器又称为相位检波器,对于占空系数为50%的对称方波可以用一个异或门来构

成,如图3-4 所示。

由异或门真值表可以看出,当异或门的两个输入端A、B 上加入两个占空比为50%的方

波时,三个输入波之间的相位在0°—180°之间变化时输出波形f 的占空比也随着变化,

如果取出波形的平均值,其值也将随着A、B 端输入波形的相位而变化,如果用R,C 构成低

通滤波器,则其传递函数为:

3、实验电路:以下为实验电路,供参考(图3-5)。静态工作点的A 点电压约在4 伏左右。

4、 沿控制比较器

它是一种适合不对称波形的相对检波器,其结构如图3-6,它是由R-S 触发器和控制门

构成。工作原理可分三个方面来分析:首先(9)、(10)门不可能同时为“1”,因为(9)、(10)门

同时为1,必须(1)、(2)、(5)、(6)、(7)输出为“0”,而要求(7)输出为“0”,则(1)、(2)、(5)、

(6)中必须有一个或一个以上为“1”,显然同前面提出要求(9)、(10)输出“1”的条件矛盾,

所以(9)、(10)不可能同时为“1”。

第二为fco 和fin 两者同时上跳和同时下跳时的状态,假定(8)、(9)输出为“0”。此时,

fin 和fco 同时上跳,则门(1)和门(6)输出为“0”,所以由(2)、(3)以及(4)、(5)组成的二

只R-S 触发器的状态保持不变,亦即门(7)的输出状态也不变,所以(8)、(9)的输出还是为“0”。

如果fin 和fco 同时下跳,则门(1)和门(6)的输出为“1”,导致两个R-S 触发器反转,使门(2)

和(5)输出为“0”,但这并不影响门(7)的输出状态,所以(8)、(9)的输出还是为“0”。

第三为fin 和fco 相位不同。假定fin 和fco 相位提前,此时门(6)的输出为“1”,所以

(4)、(5)触发器反转,使门(5)输出为“0”,所以此时门(1)、(3)、(7)均为“0”,使门(8)输出

为“1”。经过一段时间后,fco 亦上跳,使门(6)输出由“1”变为“0”,门(7)的全部输入为

“0”,所以输出为“1”,这就使二只R-S 触发器复位,并将门(8)的输出从“1”反转为“0”。

同样可以分析当fin 相位滞后于fco 时,将在fco 上跳时使(9)为“1”直到fin 上跳到

来时才使(9)为“1”。

总之,当fin 超前fco 时,(8)出现一串脉冲,(9)为“0”,当fin 滞后于fco 时,(9)出

现一串脉冲,(8)为“0”。

图3-7 为一比例加法器,它是利用运算放大器构成,其输入端分别接到(8)、(9),在输

出端即可合成一条比较理想的鉴相曲线。

5、寻找同步范围

锁相环的工作范围可用捕捉带和保持带来表示。捕捉带和保持带的示意图如图3-8 所

示。

通常保持带宽会大于捕捉带宽,用双踪示波器观察输入、输出是否同步。按图3-8 分别

记录锁相环的捕捉带和保持带。

三、锁相环的典型应用——频率合成

CC4046 的引脚图如图3-9 所示。

锁相环的重要用途之一就是用作频率合成。所谓频率合成是指将任一给定的频率f0(通

常是由石英晶体振荡器产生的高稳定度的频率)变换成一系列新的频率f 01、f 02 ...f 0n。

这些新的频率的稳定度与基准频率相当。例如,f 0 的稳定度为10-6(即百万分之一),则

一系列新频率的稳定度也达到10-6。本实验利用CC4046 锁相环实现1KHZ—999KHZ 频率

合成。

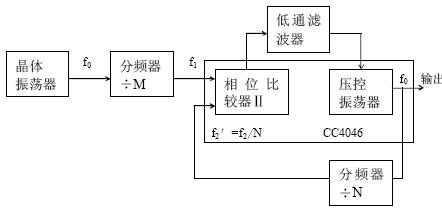

锁相环用于频率合成的原理方框图如图3-10 所示。我们已经知道,把分频器(÷N)

插在锁相环压控振荡器vco 的输出端与相位比较器的输入端之间,锁相环即可对输入频率进

行准确的N 倍频。图3-10 中,设晶体振荡器频率为f0,经过固定式分频电路(÷M)得到

基准频率f1,再送至锁相环CC4046 的相位比较器Ⅱ的信号输入端。若由压控振荡器vco 产

生的频率信号为f2,经过一个可预置数的分频器,可得到f 2′=f 2/N(N 为预先设定的分频

系数),然后再送到相位比较器Ⅱ的比较信号输入端。当CC4046 相位锁定时,有关系式f 2

′=f 1,即f 2/N= f 1,则f 2=N f 1。此时,锁相环输出信号的频率是输入信号频率f 1的N 倍。

图3-10

图3-10

如果分频系数N 是可变的,N=N1、N2⋯ ⋯Nn,例如能从1 连续变化到999,这时即

可得到999 个不同的f 2 输出,从而实现了频率合成。

频率合成的一种实用电路如图3-11 所示。本电路可输出1KHZ—999KHZ 范围内,间隔

为1KHZ 的999 种标准频率。图3-11 电路看起来比较复杂,但与图3-10 对照来看,就可明

显的看出它由基准频率产生,锁相环及分频器÷N 三部分组成。

基准频率产生部分采用JA9 型100KHZ 金属壳石英谐振器与六反相器CC4049(只用了

其中三个反相器)组成晶振和放大整形电路,得到100KHZ 的矩形脉冲。再经过双二——

十进制同步计数器CC4518 完成100 分频,以获得1KHZ 的基准频率f 1。f 1 经CC4046 的

第14 脚送至相位比较器Ⅱ。然后从vco 输出信号f 2。

我们已经知道,在vco 的输出端4 与相位比较器的输入端3 之间插入一个分频器(÷N),

就能起到倍频作用,使vco 的输出信号频率f 2=N f 1。若设N=175,则f 2=175×1KHZ=

175KHZ。

图中用三块CC14522 可编程1/N 计数器和三只8,4,2,1 编码的拨盘开关组成。有

关拨盘开关的原理,可参看无线电1986 年第8—9 期的有关文章。

如果分频系数N 是个三位数,则可表示成N=100N3+10N2+N1,这里的N1、N2、N3

分别代表个位、十位、百位上的数字,也就是拨盘开关KA1、KA2、KA3 上分别设定的数

值。因此使用三只拨盘开关,即可组成001 到999 范围内的任何数。例如,按图2 所示,将

KA3 拨至数字1,数字1 对应的BCD 码位0001,所以前三个开关断开,最后一个开关闭合。

同理,将KA2 拨至7(0111),KA1拨至5(0101),各开关即如图3-11 所示状态,就可得到分

频系数N=100×1+10×7+1×5=175。当然N 也可以设定001—999 中的其他值。由于每

设定一次,就相当于给1/N 计数器编一次运算程序,因此称它为可编程1/N 计数器。

该计数器的个位、十位、百位分别是CC14522Ⅰ、CC14522Ⅱ、CC14522Ⅲ。电路采用

正逻辑,即“1”为高电平(VDD),“0”为低电平(VSS)。在介绍其工作过程之前,先对各端

子做一些简单的说明。

CC14522 型计数器的CP 端和EN 端均为输入脉冲端。电路规定:当EN 端接“0”电平

时,输入脉冲应加至CP 端,且用脉冲的上升沿触发;当CP 接“1”电平时,输入脉冲应加

至EN 端,此时用脉冲的下降沿触发。在图3-11 中,选定从CP 端输入脉冲,所以EN 端固

定接地为“0”电平,从vco 输出的信号作为输入脉冲加到CC14522Ⅰ的CP 端。

每块14522 的D1—D4 端是预置数输入端,PE 是预置允许端。以个位14522Ⅰ为例,当

PE=1时,不管原来的计数状态如何,可立刻将拨盘开关KA1 设定的5(0101)从D1—D4 端置

入计数器。

CC14522 的Cr 端是复零端。当Cr=1 时,能强迫计数器复零,计数电路停止工作。图

3-11 中的Cr 端固定接“0”电平,可使电路循环工作下去。

计数器的Oc 端是全“0”信号输出端,仅当计数器状态为“0000”,且CF 为“1”时,

Oc 才输出“1”。CF 是级连反馈端,它们分别与前一级的Oc 端相连。这样当前级计数器为

“0000”状态时,其Oc=“1”的信号就反馈到下一级的CF 端,使CF 为高电平。

三级计数器的PE 端与个位计数器的Oc 端相连。这样,当个位计数器状态从5 一直减

到0(相当于完成一次÷5 运算)时,CC14522Ⅰ为“0000”状态。由于个位计数器的级连反馈

端CF 与十位计数器的Oc 端接通,若假定十位计数器也是“0000”状态Oc=1,此信号就送

到各位计数器的CF 端,使之也为高电平。对个位计数器而言,由于CF=1,并且计到“0000”

状态,因此从Oc 端输出高电平信号,这个高电平信号,一方面作为第二次置数信号(PE=1),

另一方面作为f2′的输出端。

应当说明,上面讲的除法运算,实际上是通过连续做减法来实现的。例如,假定N=175,

即N1=5,N2=7,N3=1。分频器的工作过程是:首先是把D1—D4 端的预置数175 分别置入

个位、十位和百位计数器。由图3-11 可见,三个拨盘开关的A1、A2、A3 是接VDD 的,个位

开关KA1 中4 刀和1 刀接通,且接至CC14522Ⅰ的D3、D1 端,因而D3、D1 端为高电平“1”。

而D2、D4 端未接通VDD,故为低电平“0”。这样8421 码的0101(数字5)就送入了D1—D4 端。

同理,8421 码0111(数字7)送入CC14522Ⅱ的D3、D2、D1 端。8421 码的0001(数字1)送入

CC14522Ⅲ的D1 端。

计数器完成预置后,从个位计数器开始做减法运算。VCO 的输出信号是一串脉冲,CP

端每输入一个脉冲,CC14522Ⅰ就自动(这是由集成电路内部控制的)减1,这时预置数5 减1

变为4。输入5 个脉冲(减5 次)后,即为0000。

当第六个脉冲到来时,CC14522Ⅰ从Q4 端向十进制计数器CC14522Ⅱ的CP 端借1,这个

1 对于个位来说相当于10,这时CC14522Ⅰ可从0000 直接变成1001(数字9)。而CC14522

Ⅱ因送出一个高电平借位信号,而从预置数7 中减去1 变成6。这样继续下去,连续减75

次以后,十进制计数器也变成了0000。当第76 个脉冲来到时,百位计数器减1 变成0,它

的Oc 端变成高电平,与它相连的CF 端也变成高电平。直至十进制计数器也减成0 时,CC14522

Ⅱ的Oc 端和CC14522Ⅰ的CF 端也均为高电平。再等个位计数器也减为0(这时共减了175

次)时,个位计数器的Oc 端才变成高电平,输出一个脉冲。由于每输入175 个脉冲,个位计

数器的Oc 端才输出一个脉冲(即前面所说的f2′信号),Oc 端就是分频器的输出端,故也就

完成了175 分频。因此,f2′=f2/175。f2′接至CC4046 的第3 脚,相位比较器Ⅱ经过对f1

和f2′进行相位比较,产生误差电压UX,滤波后得到控制电压Ud,去控制VCO 的输出频率。

当相位锁定时,对于上面的例子,VCO 输出的是高稳定度的175KHZ 的基准频率。

为便于读者阅读,图3-11 中标明了锁相环中各信号的去向。电路中拨盘开关选用KA

型按键式开关,利用按键代替手拨转轮,操作非常方便。

除此以外,锁相环还可用作电压——频率(V/f)转换器(单独使用锁相环中的压控振荡

器,即可构成V/f 转换器)。利用锁相环还可以对调频信号进行解调,从中取出音频信号。

目前,国外已把锁相技术应用到彩色电视机的电路中,例如,法国汤姆逊TFE5114DK 型20

英寸彩电。

- 相关推荐

- 热点推荐

- 锁相环

-

锁相环频率合成器的特点和应用2024-08-05 2257

-

基于ADF4111的锁相环频率合成器设计2023-10-20 508

-

锁相环频率合成器的优缺点2023-09-02 3697

-

锁相环频率合成器是什么原理?2021-04-22 2575

-

如何采用CD4046实现锁相环频率合成器的设计?2021-04-12 2096

-

一种基于ADF4106的锁相环频率合成器应用实例介绍2019-07-04 3856

-

基于ADF4106的锁相环频率器研究与设计2015-10-17 2782

-

锁相环技术在频率跟踪中的应用研究2010-07-29 902

-

集成锁相环频率合成器,什么是集成锁相环频率合成器2010-03-23 954

-

锁相环频率合成器的方案研究2010-03-16 4991

-

基于ADF4106的锁相环频率合成器2009-05-05 3046

全部0条评论

快来发表一下你的评论吧 !