利用Verilog硬件描述语言实现DVB-H系统载波同步的设计方案

描述

1、引言

多数手机电视标准采用了OFDM 技术,但对于OFDM信号,载波频偏将破坏信号子载波问的正交性,引入载波间干扰.一个小的频偏就可能导致SNR的降低,所以,在OFDM的手机电视系统中,精确估汁并校正载波频率偏差是非常重要的一部分。

以DVB-H系统为例,整数倍频偏采用连续导频进行相关估计的算法,小数倍频偏采用通过整数倍频偏估汁修正与估汁值自平均相结合的算法,同时给出了硬件实现架构。

2、基于DVB-H的载波同步方案

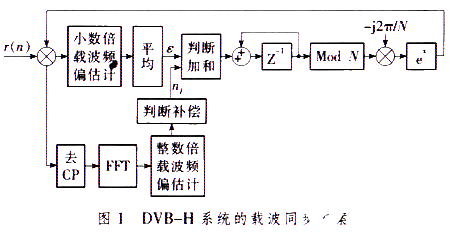

系统的载波同步的算法一般都是基F信号帧结构中的已知信息。以DVB-H系统为例,其信号帧结构中的已知信息为时域上的循环前缀CP以及频域上的按固定规律出现的连续导频和离散导频。因此通常在FFT前用循环前缀粗估计小数载波频偏的值,而在FFT之后用连续导频或离散导频检测整数倍载波频偏值以及精细估计小数倍载波频偏的值。但是这种传统算法精细估汁小数倍载波频偏计算复杂度高,硬件实现复杂。本文采用了一种用循环前缀估汁小数倍载波频偏,FFT后用连续导频估计整数倍频偏,同时对小数倍频偏进行修正的方案,简化了汁算复杂度,易于硬件实现、本方案综合考虑了估计精度和硬件的可实现性,如图1所示。

在时域上基于CP对小数倍载波频偏的快速捕获,通过平均模块对连续n帧得到的估计值ε进行平均,进一步减小随机噪声的影响。FFT之后,在频域上利用相邻两个OFDM符号的连续导频信号进行相关估出整数倍载波频偏,并判断小数倍载波频偏是否在±0.5以内,对在时域上估计的小数倍频偏进行修正。频域估计得到的整数倍载波频偏估汁值反馈到接收信号的时域端,与平均模块后的小数倍载波频偏估计值相加进行载波频偏补偿。

2.1小数倍载波频偏估计算法

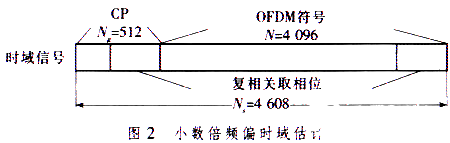

在发送端,循环前缀是每帧有效数据的最后一部分的复制,如图2所示。循环前缀与每帧有效数据的最后一部分幅值相同,区别是有一个相位的旋转,这个相位正比于载波频偏,可根据这个相位旋转估计得到小数倍载波频偏。

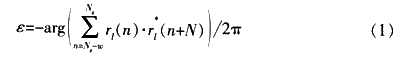

具体算法为利用循环前缀开窗与数据进行相关,为尽量减少其受上一帧数据污染的可能性,开窗的位置越靠后越好。相关值在开窗范围内做平均取相位再除以-2π便可求得在多径信道情况下估计得到的小数倍载波频偏

式中:ω为开窗长度。

2.2整数倍载波频偏估计算法

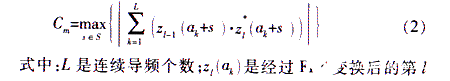

在小数倍频偏进行估计和补偿之后,载波频偏在频域上的一个主要影响表现在子载波的循环移位,可利用处于每帧OFDM符号中特定子载波位置上的连续导频来进行载波频偏的估计。由于连续导频在每一帧中的固定位置上出现,自相关性好,对连续两帧OFDM符号在连续导频的位置进行复相关并求和,使用一个长为S的滑动窗作为频域上子载波有可能的相对偏移范围,这样得到S个相关值,其中最大相关值所对应的s即为频域上子载波的相对偏移,即整数倍载波频偏的估计值

个符号的第κ个连续导频位置上的复数值;S是整数倍频偏的估计范围;s是窗口移动值,s∈S;S路相关和的最大值Cm对应的s即为整数倍载波频偏的估计值m。

2.3小数倍载波频偏修正算法

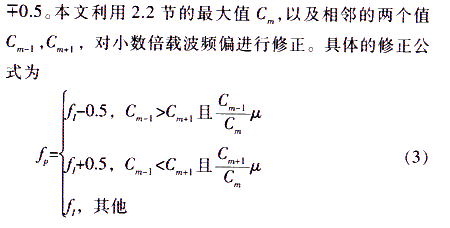

如果小数倍频偏在±0.5以内时,仅用2.1节算法的估计值与实际值相比有可能出现跳变,即+0.5估计成

式中:μ为预先设定的阈值,一般设为0.2,经过整数倍频偏估计对小数倍频偏的补偿处理,一般可使剩余的小数倍频偏在-0.25~+0.25之间,这样可避免小数倍载波频偏在+0.5内估计出的ε存在跳变的可能,以提高估计的准确度。

3、DVB-H载波同步的硬件实现

3.1小数倍载波频偏估计的硬件实现

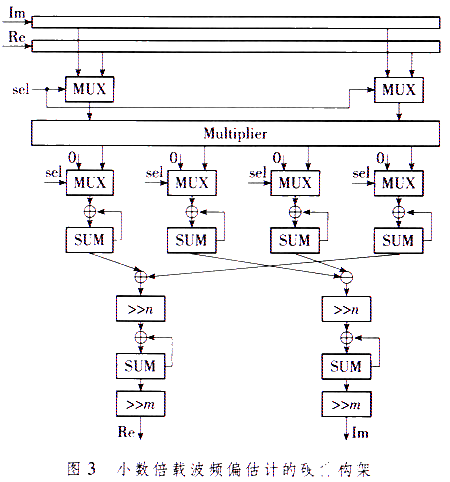

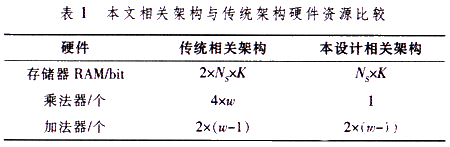

根据2.1所述的算法原理及公式(1),假设开窗长度为ω,OFDM符号长为Nc,每个有效数据为K bit,对于每个OFDM符号要进行4×w次乘法,2×(ω-1)次加法,同时要两块RAM,每块容量为Ns×K bit,一块存储当前OFDM符号,另一块为读取上一个OFDM符号的内容进行相关运算。 图3的硬件构架,考虑到每次估计之间的时间间隔为Ng个时钟(循环前缀CP的长度),足够进行相关运算,因此可对RAM进行复用。同时通过选择控制信号对乘法器进行复用,仅要一个乘法器就可实现运算。

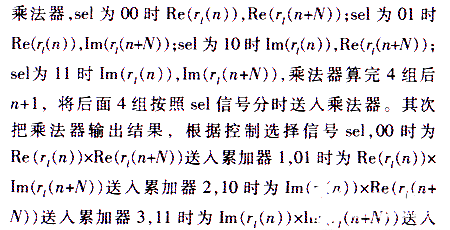

首先产生控制信号,选择窗内数据的实部,虚部分别依次存入长为64的FIFO,此处窗长设为64。根据控制选择信号sel,用流水方式将下面4组信号分时送入

累加器4进行累加。一帧估计完后,把累加器1与累加器4的值再送入加法器得出估计的实部,把累加器2与累加器3的值送入减法器得出估计的虚部。然后对估计值做平均,为了硬件实现方便,窗长选为64,因此将结果送入移位器右移6位,即可对累加结果做平均。最后对连续8帧的估计值,通过累加器移位器累加并右移3位做平均,进一步降低随机噪声的影响。表1比较了本设计与传统相关架构的硬件资源。

由表1可见,本文架构在加法器数量不变情况下,存储器容量节省一半,特别是对FPGA中十分稀缺的乘法器资源,节省了4w-1个,相关窗越长节省的数量越大。

3.2整数倍频偏估计及小数倍频偏修正的硬件实现

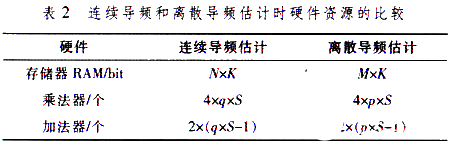

对于整数倍载波频偏估计来说,输入数据去掉循环前缀CP,再经过FFT得到频域数据,可利用连续导频或离散导频估计载波频偏,两者均采用相关的方法。表2比较了连续导频和离散导频时所需硬件资源的情况。

表2中Ⅳ为一个OFDM符号中的子载波的个数;M为离散导频循环一次所包含的子载波个数;K为每个子载波信号的比特数;q为一个OFDM符号中连续导频的个数;p为离散导频循环一次所包含的离散导频的个数,S为滑动相关窗长。一般有M》N,p》q,因此离散导频整数倍载波频偏估计的算法比连续导频的估计算法要用到更多的存储器、乘法器和加法器资源。连续导频的方法已能准确地估计出整数倍载波频偏,不必再用离散导频的算法来进行整数倍载波频偏估计。

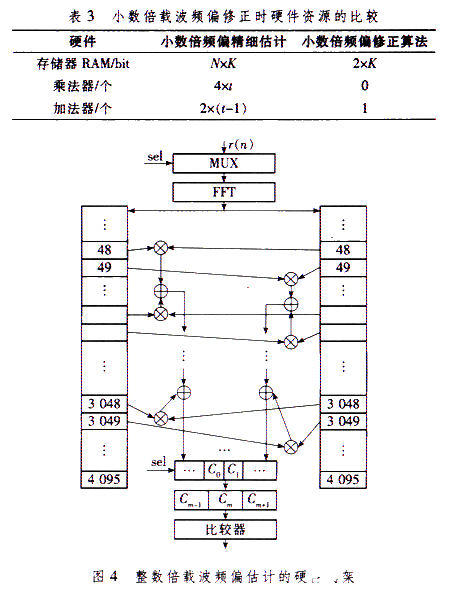

对于小数倍载波频偏估计来说,如果小数倍频偏在±0.5以内时,估计值和实际值相比有可能出现跳变,要想准确估计,通常需要许多个OFDM符号利用连续导频或离散导频进行精细估计。而本文对小数倍频偏估计采用通过整数倍频偏估计修正与估计值自平均相结合,由于利用了整数倍载波频偏估计中的运算结果,并通过合理的设置参数,仅需用一个移位器,一个加法器和一个比较器就可在保持一定精度的前提下大大节省运算量。

表3中的Ⅳ为利用连续或离散导频进行小数倍频偏精细估计一次所利用的子载波个数;K为数据的比特数;t为进行一次估计所用的连续或离散导频数。从表3可以看出利用连续导频或离散导频对小数倍载波频偏进行精细估计,硬件实现计算复杂,十分耗费资源。而利用本文的通过整数倍频偏估计修正算法可以大大节省硬件资源。 整数倍载波频偏估计的硬件实现构架如图4所示。首先对输入的数据送入选择器去除循环前缀CP,送人

FFT模块;为了运算的速度和数据的连续性使用乒乓操作,在第一个缓冲周期,将连续两帧数据缓存到数据缓冲模块1,2,在第二个缓冲周期通过输入数据选择信号将其后的两帧数据缓存人数据缓冲模块3,4,同时把在第一个缓冲周期存入数据缓冲模块l,2的数据送入数据运算模块进行运算处理,如此循环进行。运算模块的具体运算过程如下:将连续两帧信号存入两个深度为4 096的RAM中,依次读出连续导频在滑动相关窗内的数,并把这些数存入寄存器进行相关。例如图4中对于一组连续入移位器左移5位,与C。送入减法器,比较符号位就可以得出频偏补偿的结果。

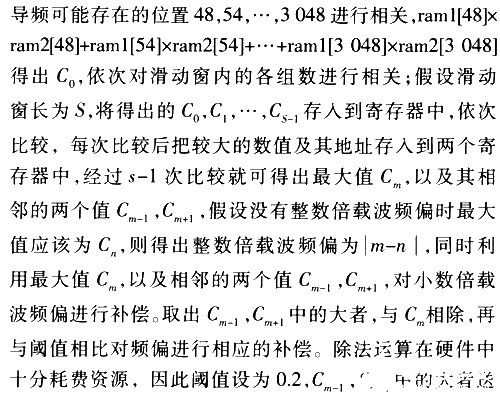

3.3载波频偏补偿的硬件实现

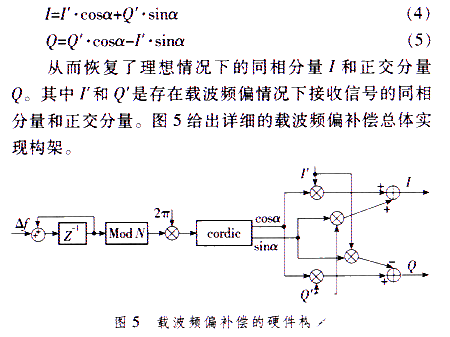

把频域估计得到的整数倍载波频偏估计值反馈到接收信号的时域端,与平均模块后估计的小数倍载波频偏估计值相加构成△f进行补偿。时域上的相偏补偿是乘以一个相反的相位α,可推导得到

首先,估计出的载波频偏经过累加器、取模器、乘法器得到

,然后经过cordic模块计算得到其正弦、余弦值,最后根据式(4),(5)进行补偿,同相分量与余弦值送入乘法器得到的值送入寄存器1,同时正交分量与正弦值送入乘法器,得到的值送入寄存器2,寄存器1和寄存器2的值送入加法器得到无载波频偏的同相分量;正交分量与余弦值送入乘法器得到的值送入寄存器3,同时同相分量与正弦值送入乘法器得到的值送入寄存器4,寄存器3与寄存器4的值送入减法器得到无载波频偏的正交分量。

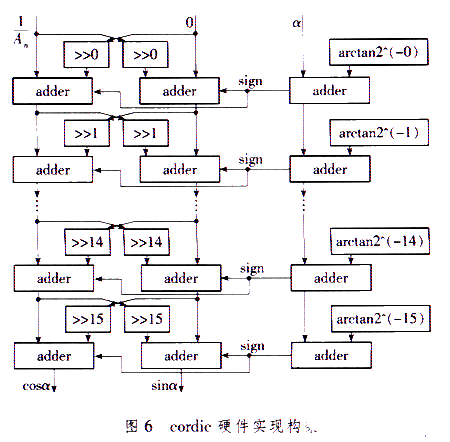

其中正弦和余弦值的计算采用cordic算法代替查找表,保证了一定的精度的条件下大大节约了存储资源。图6为cordic硬件实现构架。

4、 小结

本文基于已有的算法,以DVB-H系统为例,对其载波同步提出了一种方案及硬件实现架构。对上述架构利用Verilog硬件描述语言进行了实现,用ModelSim SE5.7进行了仿真,同时用Quartus II 6.O进行了综合,选用芯片EP2C70F672C8。整数倍载波频偏估计模块最高时钟频率可达87 MHz,所用的M4k为48个,LE约为3 800个,乘法器为12个;小数倍载波频偏估计模块最高时钟频率可达102 MHz,所用的M4k为2个,LE约为184个,乘法器为1个;载波频偏补偿模块最高时钟频率可达73 MHz,所用的LE约为2 000个,乘法器为8个。本文提出的硬件实现架构,速度快,节省硬件资源。

责任编辑:gt

-

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计2022-08-31 3271

-

如何使用VHDL硬件描述语言实现的十六路彩灯控制系统?2021-04-19 1647

-

请问如何使用Verilog硬件描述语言实现AES密码算法?2021-04-14 1358

-

Verilog硬件描述语言的学习课件免费下载2021-01-22 1251

-

基于VHDL硬件描述语言实现CPSK调制的程序及仿真2021-01-19 965

-

基于Verilog硬件描述语言的IEEE标准硬件描述语言资料合集免费下载2020-06-18 1252

-

Verilog硬件描述语言2016-09-01 1114

-

Verilog HDL硬件描述语言2015-12-29 747

-

Verilog硬件描述语言参考手册2015-11-12 920

-

verilog硬件描述语言课程讲义2012-05-21 918

-

Verilog HDL硬件描述语言【书籍2010-07-02 880

-

VERILOG HDL硬件描述语言2009-07-20 970

-

Verilog硬件描述语言描述.2006-03-27 1602

全部0条评论

快来发表一下你的评论吧 !