24位∑-Δ模数转换器AD1555/6的功能特性和应用分析

模拟技术

描述

1 概述

AD1555 是一种过抽样∑-Δ调整器,它内含一个可编程增益放大器(programmable gain amplifier,PGA)可用于低频、大动态范围的测量领域,该器件在技术上采用模拟输入线性输出方式,它与AD1556数字滤波器/抽样器结合使用可构成一款高性能的模数转换器。由于使用了连续时间模拟调制器,因此,它们不需要外部去阶梯滤波器。此外,采用可编程增益前后简化系统的设计方法还扩大了动态范围,减小了电路板的面积。同时低功耗和备用模拟的采用更使得AD1555在电池供电数据采集系统中成为理想的应用选择。

AD1555是一种采用BICMOS器件。它是一种高性能的双极CMOS晶体管组成的模拟器件。AD1555和AD1556分别采用28脚和44脚封装。

2 引脚功能

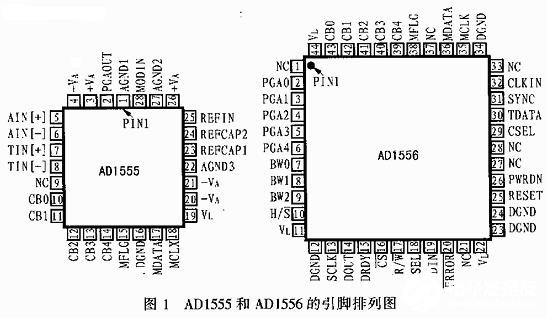

AD1555和AD1556的引脚排列如图1所示。

2.1 AD1555的引脚定义

AD1555的引脚定义如下:

AGND1(1脚):模拟地;

PGAOUT(2脚):可编程增益放大器输出;

+VA:(3,26脚):模拟电源电压正端,额定值为+5V;

-VA:(4,20,21脚):模拟电源电压负端,额定值为-5V;

AIN(+)(5脚):多路复合输入,用于输入PGA多路复合输入的非逆变信号;

AIN(-)(6脚):多路复合输入,用于输入PGA多路复合输入的逆变信号;

TIN(+)(7脚):多路复合输入,用于输入PGA多路复合输入的逆变检测信号;

TIN(-)(8脚):多路复合输入,用于输入PGA多路复合输入的非逆变检测信号;

NC(9脚):工厂自定义管脚。在正常使用状态下该引脚悬空;

CB0~CB4 (10~14脚):调整器控制端。这些引脚可用于控制AD1555的多路复合选择、PGA的增益设定以及备用模式。当AD1555和AD1556一起使用时,这些引脚一般直接和AD1556的CB0~CB4输出引脚相连接。CB0~CB2主要用来设定PGA增益或进入备用模式。CB3,CB4主要用来选择 PGA的多路复合输入电压;

MFLG(15脚):调制器的错误位,有越界信号时为高电平;

DGND(16脚):数字地;

MDATA(17脚):调制器的输出口,输出的位流信号在大约0.5个MCLK周期内有效;

MCLK(18脚):时钟输入信号,约为256Hz,当AD1555处于掉电状态时,MCLK保持不变。

AGND3(22脚):模拟地,作为REFIN引脚的参考地;

REFCAP1(23脚):DAC参考滤波器,为调制器提供参考输入,在REFCAP1和AGND3间连接一个22μF的外部钽电容可滤除外部参考噪声;

REFCAP2(24脚):参考滤波器;

REFIN(25脚):参考输入;

AGND2(27脚):模拟地;

MODIN(28脚):调制器输入,通常直接和PGAOUT相连。

2.2 AD1556的引脚功能

NC(1,21,27,28,33,37脚):悬空;

PAG0~PGA4(2~6脚):PGA和多路复合控制输入,在重启或硬件模式时,可用来设定CB0-CB4的逻辑电位和结构寄存器中相应的状态位;

BW0~BW2(7~9脚):输出率控制端,在重启或硬件模式时可用于设定数字滤波器的抽样率和结构寄存器中的相关状态位;

H/S(10脚):硬/软件模式选择端口,高电平时为硬件工作模式,低电平时,器件被设置为向结构寄存器的写时序或连续写时序;

VL(11,22,44脚):数字电源,额定3.36V或5V;

DGND(12,23,24,34脚):数字地;

SCLK(13脚):串行数据时钟输入端,可用于使DIN引脚的写信号操作和DOUT引脚的读信号操作同步传输;

DOUT(14脚):串行数据输出,在读操作的开始时开始输出,在SCLK的上升沿时数据改变,且在SLCK下降沿之前有效;

DRDY(15脚):数据就绪,输出为高电平时,数据准备进入输出数据寄存器;输出为低电平表示读操作完成;

CS(16脚):片选端,为低电平时,引脚DIN、DOUT、和SCLK被激活;为电平时,这些引脚无效;

R/W(17脚):读/写选择,设置为高电平且CS为低电平时,激活读操作;设置为低电平时,可由DIN引脚进行写操作;

RSEL(18脚):寄存器选择,设置为高电平时,数字寄存器的转换结构由DOUT引脚输出;设置为低电平时,状态寄存器的内容由DOUT引脚输出;

DIN(19脚):串行数据输入,在读操作时,可由输入转换寄存器向结构寄存器载入,人最高位开始,在SCLK下降沿有效;

ERROR(20脚):错误标志,输出为低电平时,表示在调制器或数字滤波器中有错误存在,此时状态寄存器ERROR位置1;

RESET(25脚):滤波器重启,输入高电平时,把状态寄存器的有关错误位清零,并设置结构寄存器中有关硬件引脚的状态位(此操作应在供电状态下进行);

PWRDN(26脚):掉电硬件控制,PWRDN为高电平且SLKIN处于第一个下降沿时,处于掉电模式;

SCEL(29脚):滤波器输入选择,该脚

为高电平时,TDATA引脚作为数字滤波器的数据输入;该脚为低电平时,MODATA引脚作为输入;

TDATA(30脚):测试数据输入端,输入测试数据到滤波器;

SYNC(31脚):同步输入,通过该引脚为AD1556数字滤波器清零,以便和滤波器卷积同步;

CLKIN(32脚):时钟输入,额定频率为1.024MHz;

MCLK(35脚):调制器时钟,用于提供调制器抽样频率,以CLKIN频率的1/4抽样;

MDATA(36脚):调制器数据,该输入引脚从AD1555接收ONES-DENSITY位流并输入到数字滤波器;

MFLG(38脚):调制器错误,用于检查调制器中越界错误的存在;

CB0~CB2(43~39脚):调制器控制端,主用来设定PGA增益或引导进入PGA备用模式,CB3和CB4用来选择PGA所需的多路复合电压。

3 电路描述

3.1 AD1555的调整电路

AD1555 内部包含一个模拟多路转换器、一个全微分可编程增益放大器和一个四级∑-Δ调制器。模拟多路转换器允许从四个外部输入端选择全微分输入、内部参考地或外部满偏参考电压。全微分可编程增益放大器有五种增益设定,分别是1,2.5,8.5,34和128。五种不同的输入范围分别是16V,636mV, 187mV,47mV和12.4mV(根据引脚CB0-CB4的输入决定)。调制器运行时的额定抽样频率为256kHz,AD1555的输出位流与输入电压成比例,经有限脉冲低通数字滤波器可滤除该位流,最后通过AD1556串行接口输出24位字数据。滤波器截止频率和输出率可由片上寄存器编程或通过数据输入引脚用硬件控制。

AD1555的动态性能和等效输入噪声因不的增益和输出率而有所不同,选用PGA的不同增益设定能将系统总的动态范围扩展到146dB。

AD1555在双重模拟输入(±5V)下工作,而数字部分在+5V下工作。AD1556在3.3V或5V电源下工作。每个装置都可在低功耗及备用状态下运用。

3.2 AD1556数字滤波器

AD1556 是一个线性低通FIR数字滤波器,它取AD1555的输出位流进行过滤和抽样。由于AD1556使用一个用户可选择的7档滤波器,因而具有7种不同的抽样率,其范围从1/16~1/1024。AD1556的额定输入字率为256kbit/s,输出字率范围从16kHz~250kHz,AD1556滤波器可取得的最大带宽平坦度为±0.05dB,最大输出带宽衰叛乱为-135dB(除了OWR=16kHz外,其带宽衰减-86dB)。其带宽频率和-3dB频率分别是输出字率的37.5%和41%。AD1556所产生的噪声,甚至由于字截断产生的噪声都可能对AD1555/AD1556芯片的动态范围造成微小的影响。除了可配合AD1555使用外,AD1556还可以与其他∑-Δ调制器组合使用。

在结构上,AD1556滤波器部分的主要结构是一个二级滤波器。第二级的抽样率是4(输出字率250Hz时,抽样率为8),每个滤波器均是线性相应等波的 FIR器件。由线性对称的数据采样器求和,再经乘法器和加法器做卷积运算。其结构如图2所示。二极滤波器的结构和一级有相似之处,主要区别是使用真正的乘法器。乘法器、加法器和输出缓冲器分别为32,35,24位字宽,截断字位并不会影响AD1555/AD1556芯片的动态性能。

4 AD1555和AD1556的连接电路

AD1555/AD1556组件构成的典型应用电路连接图如图3所示。

5 结束语

AD1555是包含PGA的过抽样∑-Δ调制器,和AD1556结合使用可组成高性能的模数转换器,可应用于地震数据探测系统和自动测试等装置。

责任编辑:gt

-

数模和模数转换器2009-09-16 7931

-

高精度模数转换器ADS1271的技术特性2019-06-14 3719

-

ADC0809模数转换器主要特性2021-12-02 3626

-

新型 24位模数转换器 ADS1210(下)2009-04-24 1173

-

单片机与AD1555 AD1556的接口和软件设计2009-05-15 702

-

使用带模数转换器的八位微控制器PIC16C711的模数转换器2009-06-29 911

-

8通道24位模数转换器ADS1216原理及应用2009-08-02 819

-

16/24位、超低噪声PGIA模数转换器CS5531/32/2010-04-28 1226

-

24位模数转换器AD7713及其应用2009-03-14 1794

-

8通道24位∑型模数转换器ADS1256原理及特点2016-06-06 1552

-

高信噪比和失真的双16位/24位高精度Δ-Σ模数转换器2018-06-07 6084

-

AD1555/AD1556:24位Sigma-Delta ADC数据表2021-04-17 1034

-

LTC2440:24位高速差分ΔΣ模数转换器2021-04-26 1043

-

24位模数转换器SC1641——AD7793的优质国产替代方案2025-01-15 1921

-

AD1555/AD1556:24位低噪声PGA ADC的卓越性能与应用解析2026-04-03 307

全部0条评论

快来发表一下你的评论吧 !