vhdl转换为verilog_VHDL和Verilog谁更胜一筹

EDA/IC设计

描述

vhdl转换为verilog

今天给大家分享一个VHDL和Verilog的工具。

很多新手初次学习FPGA都曾遇到过一个问题:是学Verilog OR VHDL?

很多初学者最终选择了Verilog,因为:

VHDL比较严谨,入门难;Verilog比较自由,容易快速掌握;

用Verilog的越来越多,VHDL越来越少,我感觉这绝对是一个趋势。国内的许多IC设计公司,Verilog也已经成为了主流设计语言。

Verilog代码运行速度快,simulation performance 好,所以netlist都用verilog,VHDL package 比较好,但写得费事。

IP供应商的IP核大多使用Verilog HDL,可找到的成熟Verilog设计比较多。

然而当前的现状却是:

并不是所有能找到的设计都是使用Verilog的,总有一些多年前的代码、IP核使用VHDL设计,但目前还在使用。

现在好多FPGA设计软件和仿真软件都支持混合设计,也就是说你的设计中可以有的模块使用Verilog设计,有的模块使用VHDL设计

其实VHDL与Verilog的语法是很固定且很简单的,对于编程有经验的人来说并不会纠结选Verilog和VHDL,两种语言完全是相通的,如果放开点说完全是一模一样的,换汤不换药。所以肯定可以将Verilog和VHDL语法之间相互转换。

可如果你只会Verilog,但是你拿到的设计是VHDL怎么办,不要担心,现在我教大家如何进行将Verilog和VHDL相互转换。

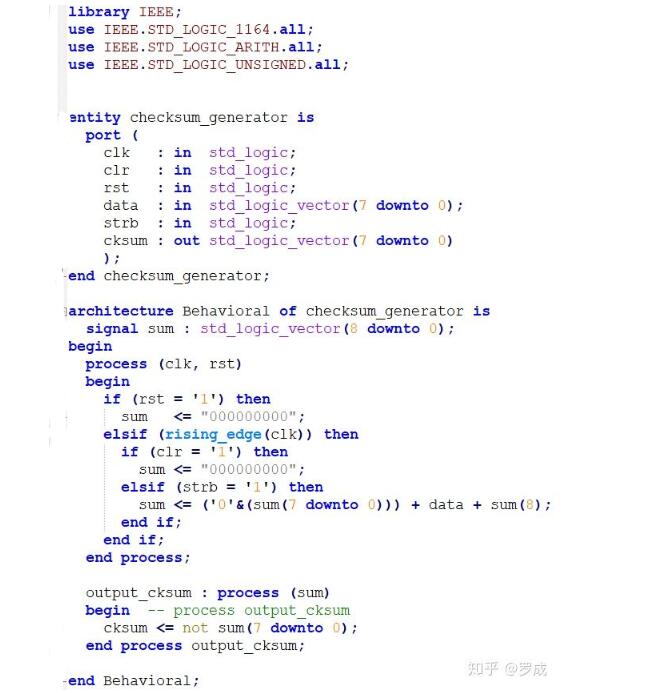

以下面一段VHDL代码为例,将其转换成Verilog,

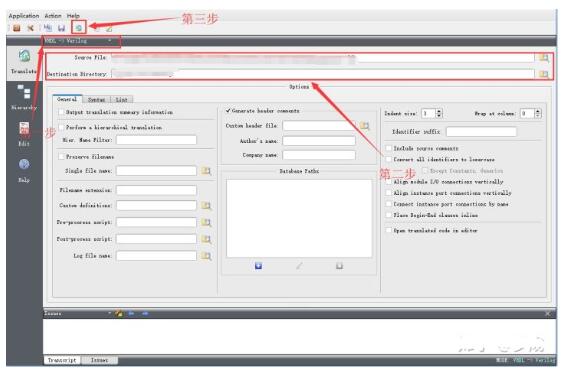

我们使用下面的小工具将VHDL转换成Verilog

第一步:选择转换模式,可以VHDL-》Verilog,也可以Verilog转VHDL

第二步:选择要转换的VHDL文件,和转换后生成Verilog文件的路径

第三步:点击转换按钮,几秒钟就可以转换好。

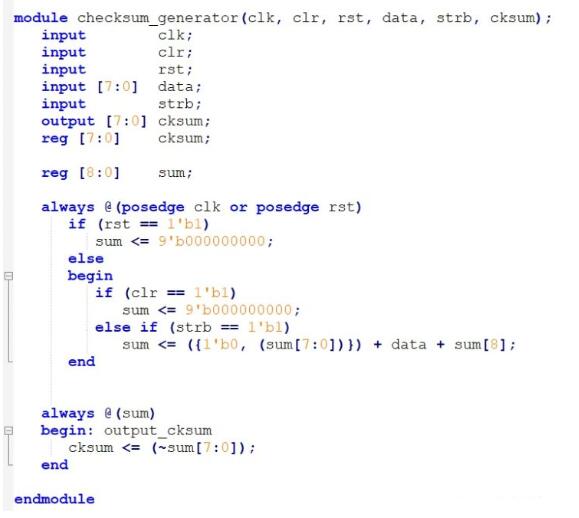

下面是转换后的效果:

转换出来的格式是不是很漂亮,看着很舒服呢!即使复杂的状态机也能转换的明明白白!

VHDL和Verilog谁更胜一筹

这两种语言都是用于数字电子系统设计的硬件描述语言,首先要明确的是VHDL、Verilog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Hardware Description Language的缩写,中文名称是“硬件描述语言”。也就是说HDL并不是“硬件设计语言(Hardware Design Language)”。别看只差这一个单词,正是这一个单词才决定了绝大部分电路设计必须遵循RTL的模式来编写代码,而不能随心所欲得写仅仅符合语法的HDL代码。这两种语言都已经是 IEEE 的标准。那么VHDL VS Verilog哪个更胜一筹呢?

共同点:

现在我们来看看这两者有哪些共同的特点:

1. 能形式化地抽象表示电路的行为和结构;

2. 支持逻辑设计中层次与范围地描述;

3. 可借用高级语言地精巧结构来简化电路行为和结构;具有电路仿真与验证机制以保证设计的正确性;

4. 支持电路描述由高层到低层的综合转换;

5. 硬件描述和实现工艺无关;

6. 便于文档管理;

7. 易于理解和设计重用

区别:

两者各有各的特点。 Verilog HDL 推出已经有 20 年了,拥有广泛的设计群体,成熟的资源也比 VHDL 丰富。 Verilog 更大的一个优势是:它非常容易掌握,是类C语言,只要有 C 语言的编程基础,可以通过比较短的时间掌握这种设计技术。而 VHDL 设计相对来说要难一点,是类ADA语言,这个是因为 VHDL 不是很直观,需要有 Ada 编程基础,一般认为至少要半年以上的专业培训才能掌握。

目前版本的 Verilog HDL 和 VHDL 在行为级抽象建模的覆盖面范围方面有所不同。一般认为 Verilog 在系统级抽象方面要比 VHDL 略差一些,而在门级开关电路描述方面要强的多。

Verilog code 运行速度快,仿真表现好,所以网表都用Verilog。VHDL语言比较严谨,某些语法错误在语法分析阶段就可以被发现,而Verilog和C类似语言风格比较自由。Verilog适合算法级,RTL,逻辑级,门级,而VHDL适合特大型的系统级设计。Verilog更加灵活效率更高。能用较少的代码实现相同的功能。而且拥有VHDL没有的系统函数。VHDL抽象层次较verilog略高,具有一些verilog没有的功能比如可以定义模块端口为多维数组类型、可以不指定状态机的具体编码方式等。

总结

那么对数字逻辑设计中究竟用哪一种硬件描述语言?目前在美国,高层次数字系统设计领域中,应用 Verilog 和 VHDL 的比率是 80 %和 20 %;日本和台湾和美国差不多;而在欧洲 VHDL 发展的比较好。在中国很多集成电路设计公司都采用 Verilog。

VHDL是美国军方组织开发的,1987年成为标准,而 Verilog 是 1995 年才成为标准的。Verilog 是一个公司的私有财产转化而来的。为什么 Verilog 能成为 IEEE 标准呢?

笔者认为一定有它独特的优越性, Verilog 拥有更强的生命力。而且容易入门,接受Verilog HDL代码做后端芯片的集成电路厂家比较多。如果着重于集成电路的设计,建议学习Verilog HDL语言。VHDL强调组合逻辑的综合,在各个高校用的比较多。

-

Oculus Rift与PS VR:谁会更胜一筹?2016-03-21 1529

-

如何快速在Verilog和VHDL之间互转2020-11-10 12075

-

例说Verilog HDL和VHDL区别2023-12-20 6343

-

射频技术和射频标识对比分析谁更胜一筹?2020-10-30 2140

-

Si整流器与SiC二极管:谁会更胜一筹2021-06-08 1650

-

生物识别技术有哪几种?到底哪种会更胜一筹呢?2021-06-28 2791

-

为何现在的串行通信传输方式会更胜一筹2021-10-15 2204

-

VHDL和Verilog HDL语言对比2010-02-09 10957

-

VHDL,Verilog,System verilog比较2012-01-17 2006

-

VHDL与Verilog互转的软件2016-06-03 751

-

Xilinx Sdram 参考设计:含Verilog和VHDL版2016-06-07 705

-

微软、谷歌、英特尔都发力AI,3巨头谁更胜一筹?2018-05-28 2170

-

探讨VHDL和Verilog模块互相调用的问题2021-04-30 12560

-

Verilog到VHDL转换的经验与技巧总结2024-04-28 4554

-

Verilog与VHDL的比较 Verilog HDL编程技巧2024-12-17 3483

全部0条评论

快来发表一下你的评论吧 !