以AD9249介绍其3线SPI配置的verilog实现

描述

上篇介绍了如何利用verilog 实现4线SPI配置时序,本篇将以AD9249介绍其3线SPI配置的verilog实现。

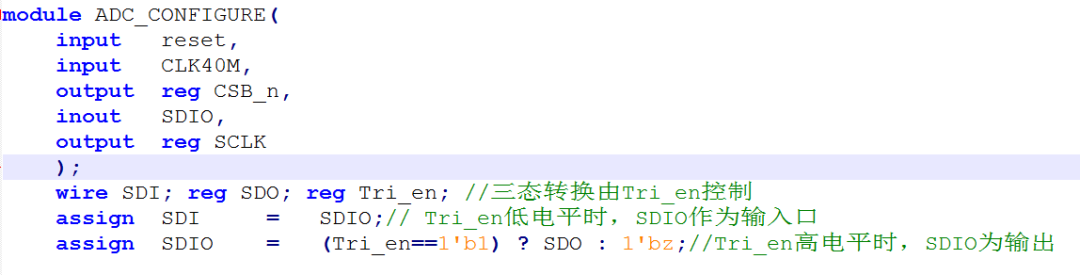

3线SPI的时钟产生方式和上一篇的4线SPI相同,这里不在叙述。两者的不同点在于:三线SPI模式需要FPGA管脚三态控制SDIO的输入/输出状态。下图所示的代码即为三态控制逻辑。SDI、SDO成为了内部逻辑信号,和上篇的4线SPI配置相同操作即可,而SDIO为三态管脚,需定义为inout类型。

Tri_en信号即为三态控制信号,在写操作中,该信号必须置高;然而在读操作中,该信号在写地址的前半段需置高,当完成写地址操作后,ADC的SDIO接口由输入变输出,此时FPGA控制Tri_en信号拉低,将FPGA端的SDIO管脚由输出变为输入,从而正常接收ADC的SDIO口输出的寄存器数值。

Tri_en到底应该在哪个具体时刻拉低,以便完成FPGA的SDIO三态转换呢?答案其实在第三篇已经说的很清楚了~~~~

另外,3线SPI读/写操作有专门的读写标志位,大家务必要留心~~

3线SPI的FPGA实现就介绍到这里了,其实和4线基本一样,只不过多了个三态转换而已,大家把上篇的4线SPI的实现过程想清楚了,再加上一个三态转换控制,3线SPI也就拿下了!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高性能16通道14位65 MSPS ADC——AD9249的深度解析2026-03-30 249

-

FPGA通过SPI对ADC配置简介(三)3线SPI配置时序分析2023-12-12 4693

-

STM32U5介绍2023-09-19 848

-

M7介绍_202106152021-08-31 715

-

EFR32介绍2021-07-23 2459

-

AD9249 ADISimADC型号2021-06-06 604

-

AD9249设计和集成文件2021-06-05 591

-

基于SPI串行总线接口的Verilog实现2021-05-29 6255

-

AD9249输入阻抗2021-05-27 906

-

AD9249 SIMULINK ADIsimADC模型2021-03-24 536

-

ADC的3线SPI配置时序2020-09-07 7986

-

AD9249 16通道、14位、65 MSPS、串行LVDS、1.8 V ADC2019-02-22 986

-

请问ad9249采的数据有多次谐波问题怎么解决?2018-07-27 2125

-

请问我的一个设计用到ad9249 ,但fpga采到的数据做fft后有很多谐波怎么解决?2018-07-24 2750

全部0条评论

快来发表一下你的评论吧 !