基于FPGA的Verilog实现VGA驱动电路

电子说

描述

VGA全称是Video Graphics Array,即视频图形阵列,是一个使用模拟信号进行视频传输的标准。分辨率高,显示速度快。

一、传输协议

VGA接口15个引脚,除去地线,我们一般会用到5个引脚:1(RED)、2(GREEN)、3(BLUE)、13(HSYNC)、14(VSYNC)。

如图1:

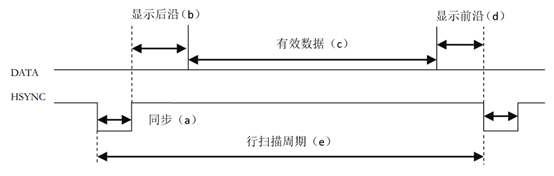

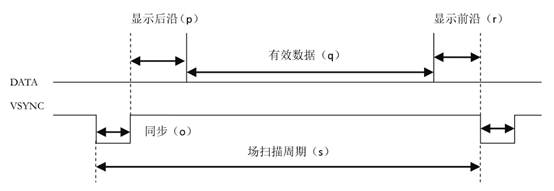

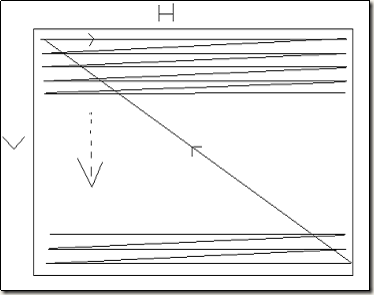

1、2、3指的是传输的红、绿、蓝三色的模拟信号,范围为0-0.714V,0代表无色,0.714V代表满色,需要注意的这是模拟信号,因此前面还需要进行一个数模转换。HSYNC(行同步信号)和VSYNC(场同步信号)分别是指传输一行和传输一帧的时序,下面看一下他们的时序图:

a:行同步时期,扫描地址的复位

b:行消隐后肩,扫描地址转移后的稳定等待准备期

c:行显示时期,数据有效区域

d:行消隐前肩,扫描地址转移的准备

e:行扫描总时间,一行扫描的总时间

o:场同步时期,扫描地址的复位

p:场消隐后肩,扫描地址转移后的稳定等待准备期

q:场显示时期,数据有效区域

r:场消隐前肩,扫描地址转移的准备

s:场扫描总时间,一场扫描的总时间

可以看出,行同步时序和场同步时序类似,分别经历4个阶段:拉低、显示后沿、有效数据传输和显示前言。

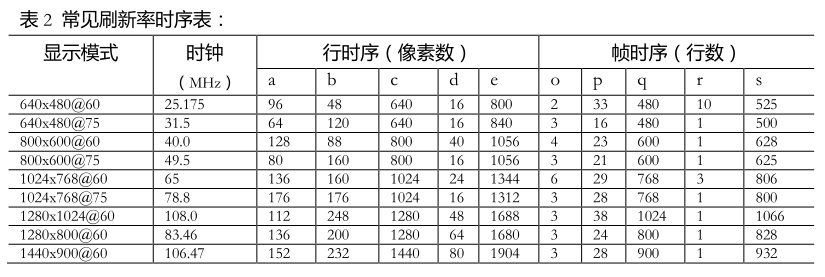

二、常见的刷新率时序表

由于FPGA擅长计数电路这里采用像素表示法来设计驱动。

FPGA硬件测试时要将sys_pll中的输出频率改为25MHZ。

三、驱动电路的verilog设计(lcd_driver)

目前液晶显示器普及,而高于 60Hz 的刷新率对于液晶来说,没有任何意义,所以我们以 640*480 在 60Hz 的刷新率下为例。

本次我们采用的是ADV7123视频转换芯片来实现。

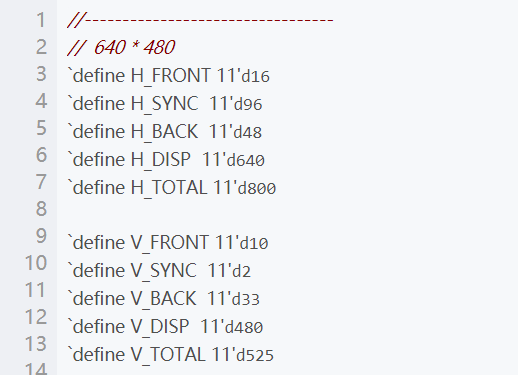

1)为便于移植,根据640*480 60hz分辨率下的参数,宏定义相关数据。

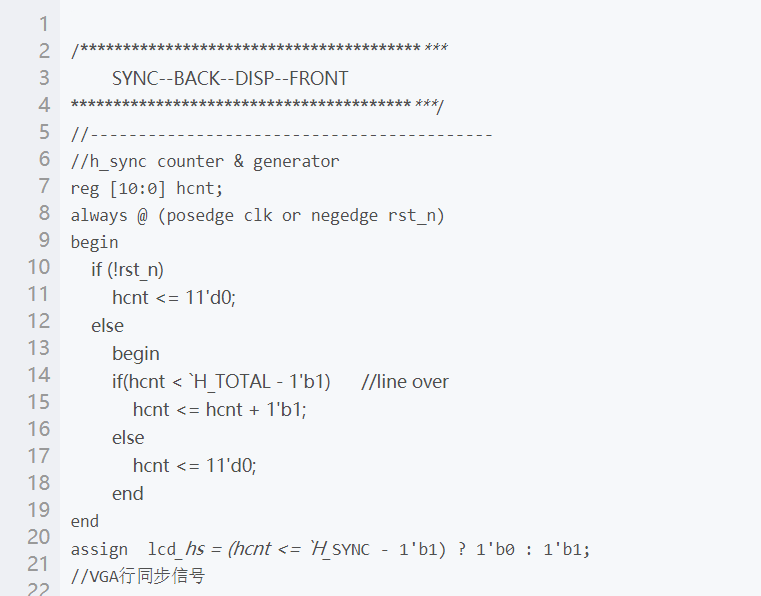

2)行扫描单位hcnt计数

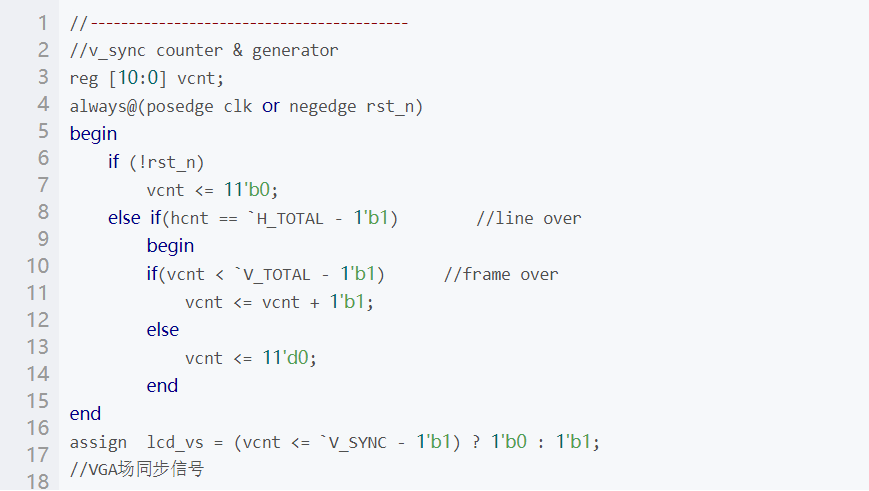

3)列扫描单位vcnt计数

每扫描完一行,即hcnt完成H_TOTAL次计数后,vcnt进行自加。

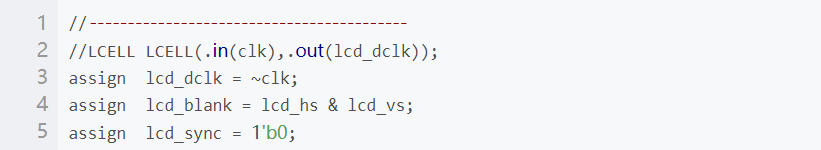

4)ADV7123控制信号输出

为了实现数据在lcd_dclk上升沿有效,我们将clk翻转输出,已实现上升沿采样 。

lcd_blank作为显示空白信号,低电平有效。

设计中不需要lcd_sync信息,可以直接接地。

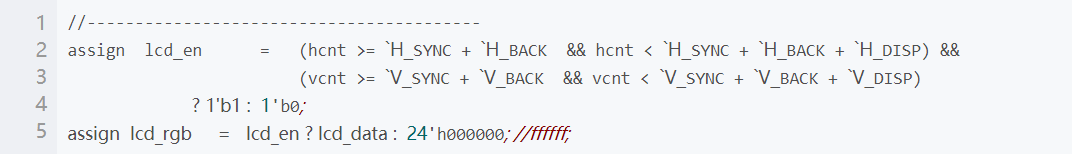

5)有效显示使能信号输出

当使能信号有效时,接收外部输入的RGB数据lcd_data.

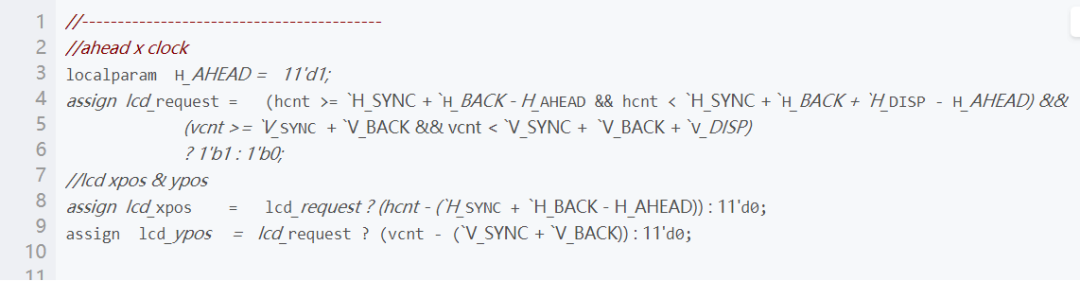

6)外部数据请求控制信号

为了保证数据稳定,lcd_request要提前一个时钟请求外部输入数据 。

同时,设计中实时显示下一时刻的扫描地址lcd_xpos、lcd_ypos,也要提前一个时钟输出,以保证外部数据输入的同步化。

lcd_xpos、lcd_ypos是显示器有效显示区域的行列坐标计数值。

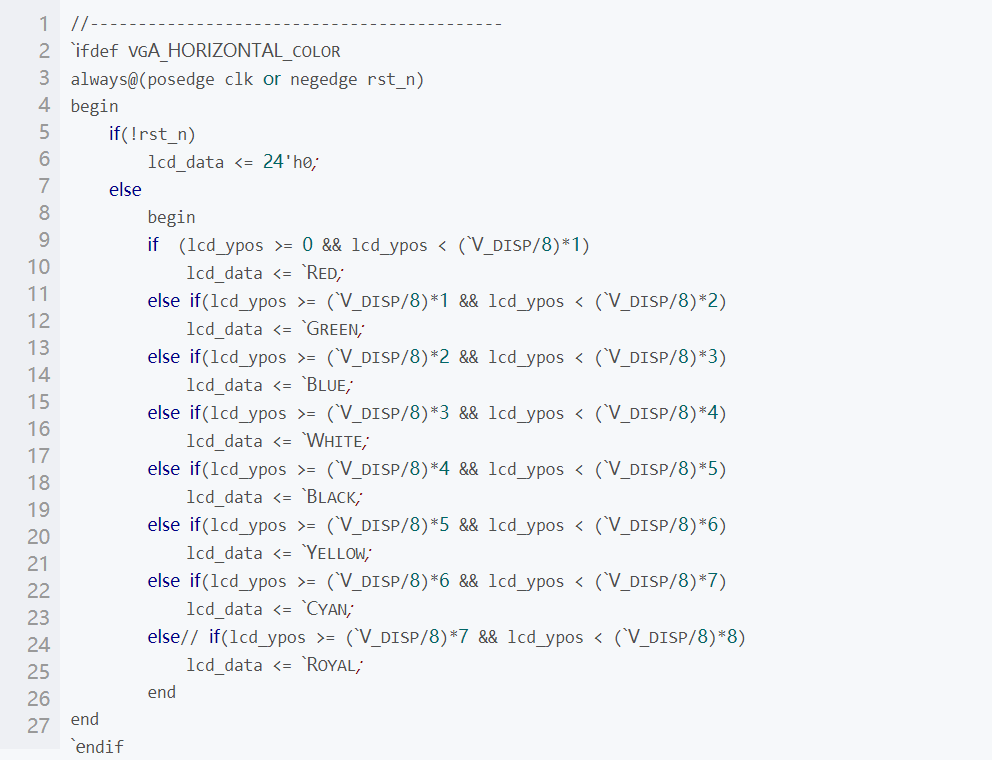

四、模拟VGA图像数据的输入

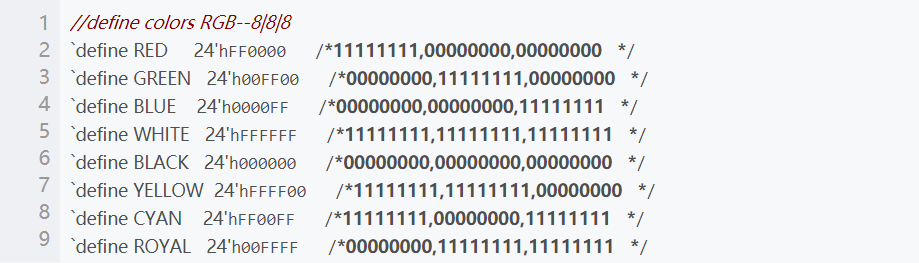

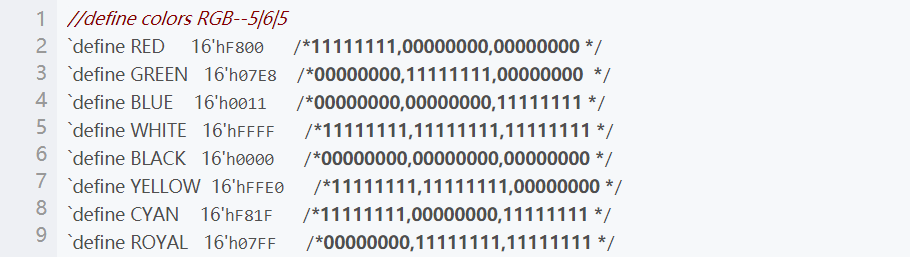

1)宏定义三原色组合的颜色如下

这里要注意所用的VGA驱动电路是RGB888还是RGB565,如果是RGB565,三原色要改成下面样式,并把其他程序中lcd_data的位数改为16位:

笔者曾在这里犯过错误。

2)根据输入的行、列地址信号,输出三原色组合后得到的8条彩色。

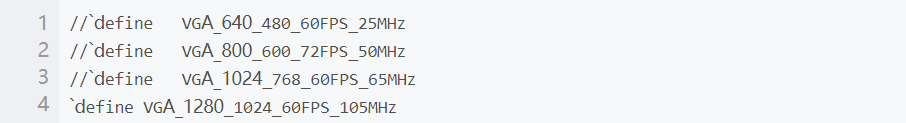

五、不同分辨率的VGA驱动

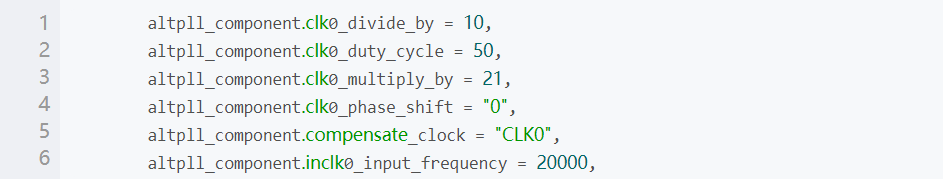

lcd_para文件定义了四种VGA分辨率驱动,这里只需修改定义的注释就行,并把PLL锁相环中的频率改为相应的频率。

PLL修改方法为直接修改下面参数中的乘法除法因子:

编辑:hfy

-

FPGA-VGA的实现资料合集2022-01-05 1016

-

ADC0809驱动FPGA实现的verilog程序2021-08-31 1475

-

FPGA设计中DAC控制的Verilog实现2021-07-26 1305

-

基于叁芯智能科技的SANXIN -B01 FPGA开发板的VGA协议驱动设计2020-09-28 3823

-

采用FPGA对VGA图形控制器的Verilog设计方法2019-06-29 6025

-

勇敢的芯伴你玩转Altera FPGA连载20:VGA显示接口电路2017-11-07 3726

-

基于FPGA的VGA图像控制器的设计与实现2016-08-30 639

-

Verilog编写的基于SPARTAN板的VGA接口显示程序2016-06-07 723

-

fpga_vga显示程序2016-03-15 926

-

数字电路中的FPGA和verilog教程2016-01-18 723

-

基于FPGA的VGA接口实现和字符显示2015-10-29 1247

-

vga贪吃蛇 verilog2013-06-11 9956

-

fpga实现jpeg Verilog源代码2011-05-27 1821

全部0条评论

快来发表一下你的评论吧 !