MOSFET阵列并联放置多个功率MOSFET以减轻系统负担

描述

在强悍的动力系统设计者应该知道所有关于MOSFET和他们的特殊电气特点,但与MOSFET的阵列工作还可以另有一个兽。您可能会在电源转换系统中看到的一种布置是并联放置多个功率MOSFET。这样可以减轻多个MOSFET的负载,以减轻系统中各个晶体管的负担。

不幸的是,MOSFET(通常是非线性元件)不能像并联一组电阻一样简单地在它们之间分配电流。就像在单个MOSFET中一样,现在热量也成为考虑因素,因为它决定了MOSFET的阈值行为(同样,这适用于任何实际的非线性电路)。为了了解这些组件在这种排列方式下如何相互作用,我们需要查看MOSFET芯片内部以及并联的功率MOSFET之间存在的寄生效应,以便防止组件自毁。

使用并联MOSFET

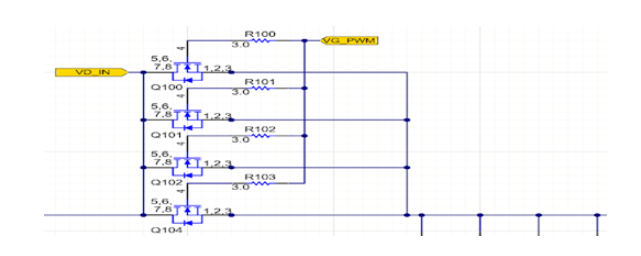

与线性或非线性其他任何组件一样,同一组件或电路网络的多个组件可以并联连接。对于功率MOSFET,BJT或原理图中的其他组件组也是如此。对于必须在两个端子上供电的MOSFET等3端子设备,所涉及的配置可能不太直观。下图显示了一个电源转换器的示例,其中四个MOSFET在转换器的输出侧并联连接。

DC-DC转换器系统中并联的四个功率MOSFET。

请注意,每个MOSFET的栅极上都有一个小电阻(稍后我将解释原因)。VG_PWM端口上还有一个来自同步驱动器的栅极脉冲,用于同时切换每个MOSFET。换句话说,这些MOSFET并非以级联方式驱动;它们被驱动使得它们全部导通并允许电流在同一时刻流动。

以这种方式连接MOSFET的优势在于,每个MOSFET均可用于向负载提供较低的电流。换句话说,假设每个MOSFET的导通状态电阻相同,则总电流在每个MOSFET中平均分配。这允许每个功率MOSFET提供高电流,同时仍具有高电流裕度,从而减少了它们产生的热量。

并联功率MOSFET的典型分析中没有包括两点:MOSFET中的寄生效应。寄生效应已经在实际组件中造成带宽限制,滤波或谐振效应。但是,当我们有多个由高频PWM信号并行驱动的功率MOSFET时,它们的寄生效应会相互影响,从而增加了开关期间产生不希望有的振荡的可能性。然后,这将显示为系统输出上的故障,并可能导致受害MOSFET过热。

并行模拟功率MOSFET

当您有多个并联的功率MOSFET时,并且您想要模拟可能产生寄生振荡的情况时,可以为您的特定MOSFET构建一个带有栅极驱动器的简单电路。确保已将适当的仿真模型附加到组件上,其中该模型包括组件中各个引脚之间的杂散电容。下面显示了一个在源侧负载的示例电路。

使用简单的栅极驱动器电路检查并联MOSFET的简单电路。

二极管D1是布置在用于NMOS晶体管的栅极驱动器电路中的1N914二极管。从这里开始,您只需要执行瞬态分析即可检查MOSFET传递给负载的电流和功率。

请注意,此模拟中涉及一些数量:

PWM上升时间:这决定了PWM信号的带宽,应与MOSFET的规格相匹配

PWM频率:具有较高频率的PWM信号会从寄生电容中看到较低的阻抗,这会将更多的功率注入到寄生反馈环路中,可能使系统谐振。

栅极电压:由于MOSFET的响应取决于栅极电压的大小,因此,当PWM信号切换并行阵列时,将产生任何寄生振荡。

您可以在瞬态仿真中轻松发现寄生电感和寄生电容的影响。下例显示了当寄生电容和电感包含在仿真模型中时,上述一对MOSFET的结果。请注意,随着PWM信号的切换,在时域响应中可以清楚地看到较大的毛刺。

开关期间MOSFET中出现毛刺。

抑制不必要的振荡和温升

如前所述,如果温度不平衡,则这些有害振荡会在阵列中的不同MOSFET中产生。换句话说,一个MOSFET的谐振条件可能不同于另一个MOSFET。如果在给定的栅极电压下,一个MOSFET在其他MOSFET之前经历了强烈的振荡,则该组件会自行损坏。因此,如果将这些组件串联连接,则最好将它们保持在相同的温度下。这可以通过在PCB布局中组件下方的大型散热器或平面层来完成。

改变谐振条件的另一种方法是在驱动电路中放置一个栅极电阻器(见上文,其中包括一个小的5欧姆电阻器)。半桥LLC谐振转换器中的MOSFET可能具有非常大的电阻器,该电阻器连接了源极和栅极以在这两个端口之间提供高阻尼。您可以试验这些电阻值,以检查它们如何影响并联电路中的阻尼。

编辑:hfy

-

mosfet并联缓冲电容2017-02-22 7070

-

功率MOSFET技术提升系统效率和功率密度2019-07-04 2644

-

如何计算MOSFET的功率耗散2021-01-11 2484

-

耗尽模式功率MOSFET的应用有哪些?2023-02-21 9847

-

功率MOSFET并联应用2010-09-30 1007

-

高频功率MOSFET驱动电路及并联特性研究2010-11-11 1849

-

功率MOSFET并联均流问题研究2009-06-30 4180

-

电平转换以控制功率MOSFET2023-02-09 1625

-

在大功率应用中并联功率 MOSFET-AN500052023-02-15 713

-

并联使用功率 MOSFET-AN115992023-03-03 680

-

MOSFET的并联使用2023-12-19 2224

-

MOSFET并联(并联功率MOSFET之间的寄生振荡)2024-07-13 628

-

成功并联功率MOSFET的技巧2024-08-29 364

-

AOS MOSFET并联在高功率设计中的应用2024-11-27 1569

-

MOSFET并联在高功率设计中的应用2024-12-04 2099

全部0条评论

快来发表一下你的评论吧 !