MOSFET寄生电容参数如何影响开关速度

描述

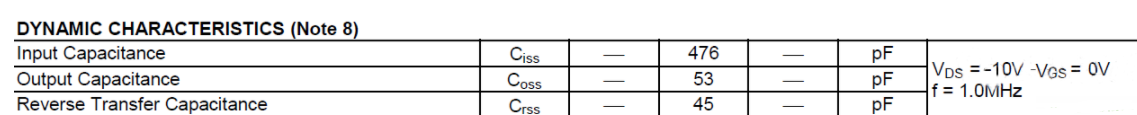

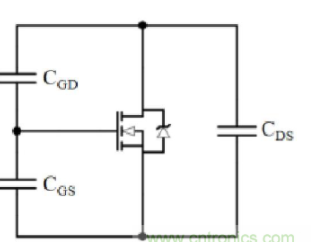

我们应该都清楚,MOSFET 的栅极和漏源之间都是介质层,因此栅源和栅漏之间必然存在一个寄生电容CGS和CGD,沟道未形成时,漏源之间也有一个寄生电容CDS,所以考虑寄生电容时,MOSFET 的等效电路就成了图 2 的样子了。但是,我们从MOSFET 的数据手册中一般看不到这三个参数,手册给出的参数一般是 CISS、COSS和CRSS(见图 1 ),

图 1 某数据手册关于寄生电容的描述

它们与CGS、CGD、CDS的关系如下:

CISS=CGS+CGD(CDS 短路时),COSS=CDS+CGD,CRSS=CGD

图 2 考虑寄生电容时的MOSFET模型

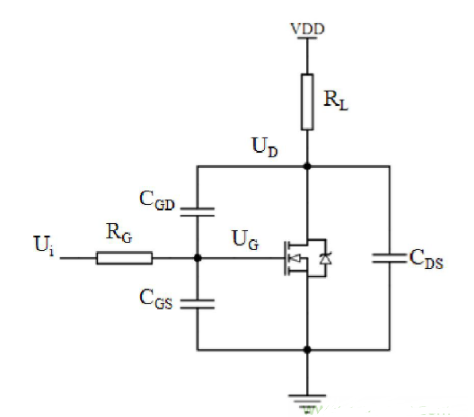

下面看一下这些寄生参数是如何影响开关速度的。如图 3,当驱动信号 Ui到来的一瞬间,由于MOSFET处于关断状态,此时CGS 和CGD上的电压分别为UGS=0, UGD=-VDD,CGS和 CGD上的电荷量分别为 QGS= 0,QGD= UGDCGD=VDDCGD。接下来 Ui通过 RG对 CGS充电,UGS逐渐升高(这个过程中,随着 UGS升高,也会伴随着 CGD的放电,但是由于VDD远大于UGS,CGD不会导致栅电流的明显增加)。当UGS达到阈值电压时,开始有电流流过MOSFET(事实上,当UGS还没有达到阈值电压时,已经有微小的电流流过 MOSFET 了),MOSFET 上承受的压降由原来的 VDD开始减小, CGD上的电压也会随之减小,那么,也就伴随着的 CGD 放电。

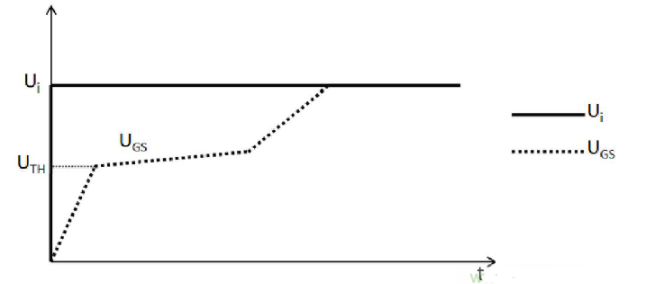

由于 CGD 上的电荷量 QGD= VDDCGD较大,所以放电的时间较长。在放电的这段时间内,栅极电流基本上用于 CGD 的放电,因此栅源电压的增加变得缓慢。放电完成后,Ui通过RG继续对CGS和CGD 充电(因为此时MOSFET已经充分导通,相当于CGS和CGD并联),直到栅源电压达到Ui,开启过程至此完成。图 4 的曲线很好地描绘了导通过程中UGS随时间变化的曲线。需要注意的是,由于驱动提供的不是电流源,所以实际上的曲线并非直线,图 4 仅代表上升趋势。

图 3 考虑寄生电容时的MOSFET驱动电路

图 4 脉冲驱动下MOSFET栅源电压上升曲线

同时,由上图 3 不难看出,RG越大,寄生电容的充电时间将会越长。显然,RG 太大时 MOSFET 不能在短时间内充分导通。在高速开关应用中(如 D 类功放、开关电源),这个阻值一般取几Ω到几十Ω。然而,即使是低速情况下,RG 也不宜取得太大,因为过大的RG会延长电容充电的时间,也就是MOSFET从关断到充分导通的过渡时间。这段时间内,MOSFET处于饱和状态(放大区),管子将同时承受较大的电压和电流,从而引起较大的功耗。但是 RG如果取得太小或者直接短路的话,在驱动电压到来的一瞬间,由于寄生电容上的电压为零,前级需要流过一个很大的电流,造成对前级驱动电路的冲击。

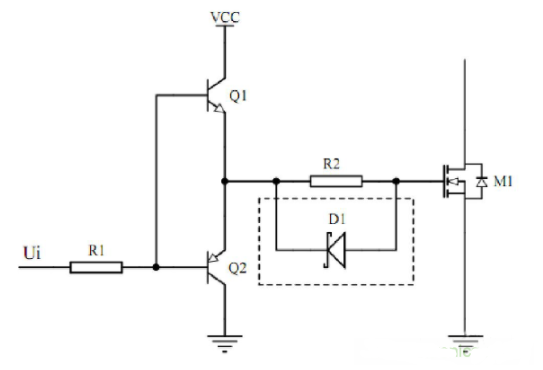

图 5 为高速开关应用中常见的 MOSFET 驱动电路,以一对互补的 BJT 构成射随器的形式满足驱动电流的要求。其中Q1用于开启时对寄生电容的充电,Q2用于关断时对寄生电容的放电。有时候我们需要得到更快的关断速度,通常在栅极电阻 R1 上并联一个快恢复二极管,这样的话,放电回路将经过这个二极管而不是电阻。

图 5 常用的高速驱动电路

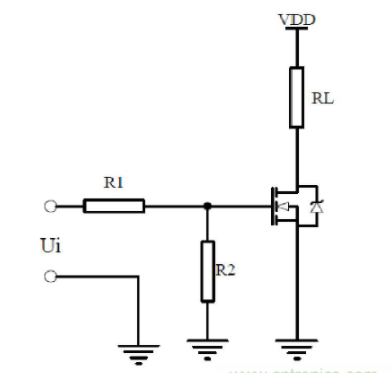

图 6 增加泄放电阻的驱动电路

在实际应用中,我们通常还会在MOSFET的栅源之间并联一个几KΩ到上百K Ω的电阻(如图 6 的R2),这是为了在输入栅源电压不确定时(如前级驱动电路失效),防止 MOSFET 处于非理性状态。

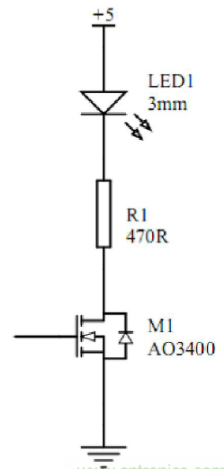

图 7 残留电荷导致MOSFET开启的实验电路

我们可以做这样一个实验:连接如图 7 的电路,我们会发现,即使栅极悬空,LED 也会发光。这说明,栅源之间出现了高于阈值的电压,产生这一电压的原因是寄生电容上的残留电荷。残留电荷使得 UGS高于阈值电压但又不足以使 MOSFET 充分导通。结果是 MOSFET 工作在放大状态(饱和区),管子承受很大的功耗从而造成器件的损坏。这种现象更容易发生在低阈值电压的MOSFET 中。为了防止这种情况发生,往往通过栅源间的并联电阻泄放寄生电容上的残留电荷。

编辑:hfy

-

普通探头和差分探头寄生电容对测试波形的影响2024-09-06 1839

-

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除2024-01-18 6734

-

SiC MOSFET 和Si MOSFET寄生电容在高频电源中的损耗对比2023-12-05 2058

-

寄生电容对MOS管快速关断的影响2023-09-17 5559

-

MOSFET的寄生电容及其温度特性2023-02-09 5173

-

什么是寄生电容,什么是寄生电感2022-07-27 20320

-

mos管寄生电容是什么2021-01-11 3125

-

什么是寄生电容_寄生电容的危害2020-09-17 33564

-

寄生电容产生的原因_寄生电容产生的危害2019-04-30 31884

-

MOSFET寄生电容对LLC串联谐振电路ZVS的影响2018-07-13 5797

-

寄生电容影响升压变压器的设计2017-05-02 2748

-

理解功率MOSFET的寄生电容2016-12-23 19097

-

寄生电容,寄生电容是什么意思2010-03-23 3240

-

PCB布线设计时寄生电容的计算方法2009-09-30 28946

全部0条评论

快来发表一下你的评论吧 !