一文详解晶圆级封装技术

电子说

描述

传统上,将单个单元从晶片中切割后再进行封装的工艺几十年来一直是封装半导体集成电路的规范方式。然而,这种方法目前没有被主要半导体制造商采用,因为高制造成本以及今天的模块的射频成分在增加。因此,晶圆级封装(WLP)的出现带来了低成本封装开发的范式转变。WLP是一种在切割晶圆封装器件之前的晶圆级封装技术。使用标准工具和工艺,WLP作为晶圆制造过程的扩展。最终,制造的WLPdie将在芯片表面上有金属化垫,并在切割晶圆之前在每个垫上沉积焊锡点。这反过来又使WLP与传统的PCB组装工艺兼容,并允许对晶圆本身进行器件测试。因此,这是一个相对较低的成本和效率的工艺,特别是当晶圆尺寸增加而芯片die在收缩时。晶圆的尺寸在过去几十年中一直在增加,从直径4、6、8英寸增加到12英寸。这导致每个晶圆die的数量增加,从而降低了制造成本。在电气性能方面,WLP优于其他封装技术,从某种意义上说,一旦WLP器件集成在密集的RF模块中,它就会导致EM寄生耦合显著减少,因为器件和PCB之间的互连相对较短,而不像在某些类型的CSP技术中使用线键合互连。

WLP芯片倒装(flip-chip)技术

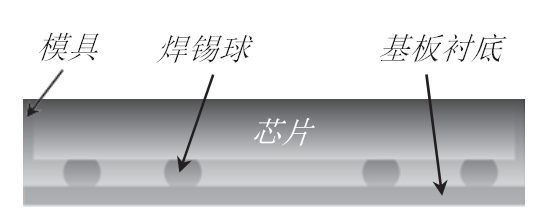

倒装(flip-chip)芯片技术也被称为控制塌陷芯片连接(C4,controlledcollapsechipconnection),是IBM在20世纪60年代开发的芯片组装技术之一。虽然基于导线键合的封装技术在硬件建成后为实验室调试提供了自由的电感能力方面更加灵活,而且还提供良好的热导特性,但使用倒装芯片封装技术使用焊锡凸起使基板和芯片之间的电气连接提供了相对尺寸减小、减少延迟以及在其输入和输出引脚方面实现更好地隔离。图1说明了芯片die在基板上的基本结构,在芯片表面生长的Cu柱顶部有焊锡球。焊点通常由填充模化合物封装,为焊点提供机械支撑。

图1、倒装(flip-chip)芯片的基本结构示例

WLP芯片级封装

芯片级封装CSP(chipscalepackaging)是微电子和半导体工业中最常用的封装方法之一。虽然有几种类型的CSP技术已经可供微芯片制造商使用,但新的类型继续出现,以满足对支持新功能和新的特定应用的产品的需求。这些包装要求可能因所需的可靠性水平、成本、附加功能和整体尺寸而不同。顾名思义,CSP的封装尺寸与芯片die尺寸大致相同,这是其主要优点之一。通过采用WLP制造工艺,CSP正在不断发展,以实现最小可能的封装-die之间的尺寸比。如图2所示,CSP在封装下的球栅阵列(BGA)风格允许有几个互连,同时简化PCB路由,提高PCB组装产量,降低制造成本。

图2、芯片级封装CSP(chipscalepackaging)的基本结构示例

其它的封装技术

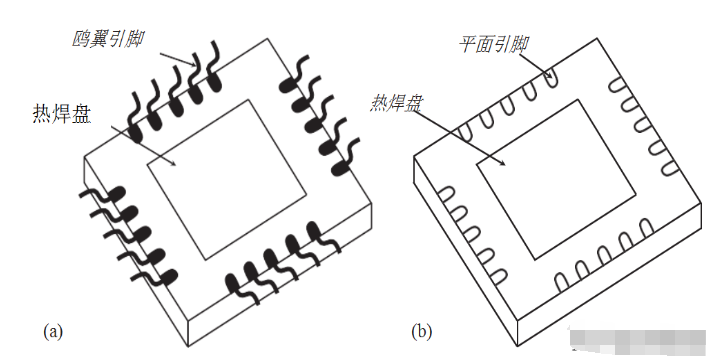

还有几种其它的集成电路封装形式,允许无缝集成到应用定制的模块封装中。四平封装(QFP,Quadflatpackage)是最早的表面贴装IC封装技术之一,其中封装的结构是由四个侧面组成的,具有扩展的互连引线,如图3(a)所示。凸起的引线连接到封装框架上,在引线和芯片die金属之间形成一个金属-绝缘体-金属(MIM,metal-insulator-metal)型的电容,可以作为匹配元件。该技术适用于毫米大小的IC,其中封装的外围引脚数量可以达到100多个引脚。这种类型的封装还存在几种衍生物,它们取决于所使用的材料,如陶瓷四扁封装(CQFP,ceramicquadflatpack)、薄四扁封装(TQFP,thinquadflatpack)、塑料四扁封装(PQFP,plasticquadflatpack)以及金属四扁封装(MQFP,metalquadflatpack)。

图3(b)所示的四平无引线(QFN,Quadflatnolead)是由平面铜引线框架和用作散热器的热传播垫的塑料封装形成的几种表面安装封装技术之一。键合线(Wirebonding)也可以用于互连,而且由于键合线不仅是导体,而且是电感,它们通常会影响在这项封装技术下器件的性能,除非它被视为整个设计的一部分。虽然QFN是由四个侧面组成的互连,但双平面无引线(DFN)也已经出现,并组成互连平面引线的两侧。

图3、集成电路封装技术:(a)四平封装和(b)四平无引脚封装

然而,我们刚才讨论的所有封装技术都不适用于当代微电子SoP和SiP。它们的使用在20世纪90年代超大规模集成电路革命期间蓬勃发展,随着更紧凑和更密集的晶圆级封装技术的出现而逐渐被淘汰。在过去几十年中,芯片和模块封装技术的发展主要是由引脚计数需求的增加所驱动的,并见证了功能、组件密度和集成水平的巨大提高。图4显示了自1970年以来集成电路封装的演变,其中双内联封装(DIP,dualinlinepackages)开始在电子IC行业发挥作用,然后出现了更多引脚的IC,如QFP,甚至更高的引脚计数技术,如引脚网格阵列(PGA,pingridarray)以及倒装芯片球网格阵列(FCBGA,flip-chipballgridarray)等。

责任编辑人:CC

-

一文详解晶圆级封装技术2023-06-25 4862

-

一文详解扇出型晶圆级封装技术2023-09-25 3139

-

晶圆级封装的基本流程2023-11-08 11562

-

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)2023-11-30 3755

-

什么是晶圆级封装?2011-12-01 16522

-

晶圆级芯片封装有什么优点?2019-09-18 5588

-

晶圆级封装的方法是什么?2020-03-06 3773

-

晶圆级三维封装技术发展2020-12-28 4209

-

晶圆封装有哪些优缺点?2021-02-23 6664

-

晶圆级封装产业(WLP),晶圆级封装产业(WLP)是什么意思2010-03-04 46759

-

什么是晶圆级封装2022-04-06 11995

-

晶圆级芯片封装技术上市公司有哪些 晶圆级封装与普通封装区别在哪2023-08-30 5755

-

一文看懂晶圆级封装2024-03-05 3423

-

详解不同晶圆级封装的工艺流程2024-08-21 4249

-

晶圆级封装技术的概念和优劣势2025-05-08 1785

全部0条评论

快来发表一下你的评论吧 !