基于FPGA技术实现安全封装双向认证方案的设计

可编程逻辑

描述

在深入分析基于FPGA的安全封装结构的基础上,针对其实际应用中身份认证的安全性要求,重点研究并设计了一种适用于FPGA安全封装结构的身份认证模型。该模型通过利用RSA公钥密码算法和SHA-1算法,实现了对用户及FPGA的双向认证。该模型具备良好的可移植性和安全性,能够有效抵御多种攻击,为基于FPGA的安全封装应用提供了强有力的用户权限认证。

随着嵌入式技术的推广,FPGA在各种嵌入式系统中得到了广泛应用。在各种嵌入式系统应用中,FPGA往往用于实现整个系统的核心功能。因此,如何保证FPGA内部功能构造的安全性成为保护整个嵌入式系统核心知识产权的关键性问题。针对FPGA内部构造码安全性的问题,各FPGA厂家推出了多种具有特殊安全功能的产品。但是,先进的数据分析技术及工具使得攻击者可以很容易地对芯片管脚的输出信号(如地址总线、数据总线)进行行为探测或数据窃取,并且根据探测结果推导出FPGA内部功能模块的实现机理。

基于FPGA的安全封装技术正是为了解决对芯片管脚输出信号的攻击而产生的一种安全防护技术,通过在FPGA芯片内的功能模块外加上一层安全封装,保证功能模块运行时的不可探测性。而作为整个安全防护机制的启用入口,身份认证机制关系整个安全封装结构的有效性,必须保证认证信息在静态存储及认证过程中的有效性及安全性。本文通过对FPGA安全封装进行剖析,重点研究并设计了一种基于FPGA安全封装的身份认证机制。该身份认证机制能够保证认证过程的有效性及认证信息的安全性,具有良好的可移植性,能够集成到各种安全封装结构中。

1 FPGA安全封装技术

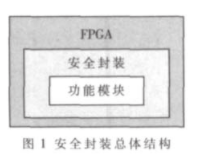

如图1所示,基于FPGA的安全封装结构可以看作是在功能模块外加上一层保护层,功能模块所有与外界的I/O端口通信都必须通过安全封装结构。当功能模块需要对外部器件进行通信时,所有功能模块接收/发送的数据均被安全封装模块进行加/脱密处理。通过这种方法,攻击者在FPGA管脚上所截获的信息均为密文信息,从而达到保护FPGA内部功能模块的目的。

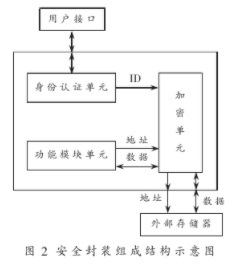

安全封装结构主要由三个功能单元组成,分别为FPGA功能模块单元、身份认证单元和加密单元。其中,功能模块单元为具体实现系统中FPGA功能的部分,是实现FPGA芯片应用的核心单元;身份认证单元主要负责对用户的合法身份进行认证并启用安全封装;加密单元负责对功能单元的输入/输出数据进行加/脱密处理,保证FPGA输入/输出数据的安全性。用户接口便于用户插入智能卡等设备,进行身份认证。安全封装组成结构如图2所示。

安全封装未启用前,FPGA芯片内的功能模块单元处于等待状态。当用户需要启用FPGA内部的安全封装时,利用智能卡与FPGA芯片进行身份认证。如果认证失败,则芯片拒绝该用户的访问,如果认证成功,身份认证单元会将用户ID发送给加密单元。接收到用户ID后,加密单元将启动功能模块单元。当功能模块单元对外部进行写/读操作时,加密单元从功能模块单元获得数据的地址信息,结合用户ID,作为产生加/解密密钥的根向量,并利用所产生的密钥对功能模块单元输入/输出的数据进行加/解密。

2 基于FPGA安全封装的身份认证

2.1 基于FPGA安全封装的双向认证方案

身份认证是通过将一个证据与实体身份绑定实现的。在FPGA安全封装应用中,实体为智能卡及FPGA。为了确保安全封装应用的安全性,在认证过程中,一方面智能卡必须向FPGA提供证据证明自己的合法身份;另一方面,FPGA芯片也必须向智能卡提供证据证明自己的合法性。因此,基于FPGA安全封装的身份认证机制必须是双向的。为了降低身份认证机制实现的复杂度并节省FPGA内部资源,选择了RSA密码算法并辅助以SHA-1算法作为实现双向认证方案的密码学基础。

RSA密码的安全性基于大合数因子分解的困难性,当大合数取1 024位或2 048位时,破译RSA密码的代价将是非常巨大的。SHA-1算法是一种单向的Hash函数,通过输入一组小于264位的报文,得到一组160位的报文摘要,并且算法满足下面两条性质:(1)通过报文摘要推算出原报文在计算上是不可行的,即算法具备不可逆性; (2)不同的两段报文所产生的报文摘要是不相同的,即算法具备抗冲击性。

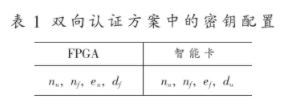

双向认证方案的密钥配置如表1所示。假设ef和eu分别为智能卡和FPGA的RSA私钥,df和du分别为智能卡和FPGA的RSA公钥,nf和nu分别为智能卡和FPGA所使用的RSA大合数。FPGA拥有自己的私钥eu和智能卡的公钥df及双方所使用的大合数nf、nu;同样智能卡也拥有自己的私钥ef和FPGA的公钥du及双方所使用的大合数nf、nu, 则双向认证过程可分为以下几个步骤:

(1) 用户将记录有用户ID信息的智能卡插入用户接口。

(2) FPGA芯片探测到智能卡的插入,启动身份认证单元。

(3) 智能卡产生一个随机数mu,并用ef和nf对其进行加密,然后将加密后的结果发给FPGA芯片中的身份认证单元。

(4) 身份认证单元使用df和nf对cu进行解密,得到解密结果mu′。

(5) 身份认证单元使用eu和nu对mu′进行加密,并将加密结果cf′回传给智能卡。

(6) 智能卡使用du和nu对cf′进行解密,并将解密结果与mu进行对比。若正确,则确认FPGA芯片对于用户的合法性,并继续下一步的操作;若不正确,智能卡将与FPGA芯片断开连接。

(7) 身份认证单元产生一随机数mf,并使用eu和nu对其进行加密,并将加密结果cf传递给智能卡。

(8) 智能卡使用du和nu对cf进行解密,得到解密结果mf。

(9) 智能卡使用ef和nf对(ID+mu+mf)进行加密,得到加密结果cID,并将cID发送给身份认证单元。

(10) 身份认证单元使用df和nf对cID进行解密,并将解密结果减去mu和mf得到ID。

(11) 身份认证单元使用SHA-1算法对ID进行Hash运算,得到chash。

(12) 身份认证单元将与ID Hash表寄存器中的值进行匹配,若匹配成功,则证明智能卡对于FPGA芯片的合法性,ID Hash将作为根向量的一部分参与到加密单元的加解密操作中去,若匹配不成功,FPGA芯片将断开与智能卡的连接。

2.2 身份认证单元模型设计

在FPGA安全封装结构中,身份认证单元的一端与加密单元相连,另一端与用户接口相连。为了满足双向认证过程中智能卡RSA运算及用户ID存储安全性的要求,选用DS1957B实现智能卡。DS1957B使用防止物理探测的封装方式,内置Java处理器、1 024位密码加速器、随机数发生器及134KB的非易失性RAM,能够非常方便地实现RSA运算,并且能够对卡内保存的密钥及用户ID信息实施密封存储。

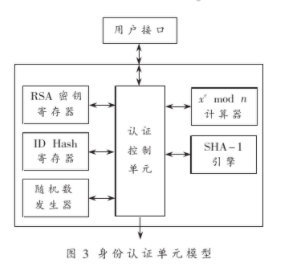

为了实现双向认证过程,FPGA安全封装中的身份认证单元模型由一个xe mod n计算器、随机数发生器、RSA引擎、RSA密钥寄存器、SHA-1计算器及ID Hash表寄存器组成。其中,xemodn计算器负责RSA密码的模幂运算,随机数发生器负责产生随机数,RSA引擎负责FPGA端的RSA运算,RSA密钥寄存器存储RSA密码的密钥,SHA-1计算器负责对用户ID信息进行单向Hash运算,ID Hash表寄存器存储合法的用户ID的Hash值。身份认证单元模型如图3所示。

3 安全性分析

身份认证单元模型的安全性主要基于三点:(1)密钥及用户ID静态存放的安全性; (2)所使用的加密算法的安全性;(3)认证方案抵御各种攻击的能力。其中第二点不属于本文讨论的范围。假定所使用的算法总是安全的,以下将具体分析第一点和第三点。

(1)针对于密钥和用户ID的静态存放,一方面由于智能卡采用了防止物理探测的封装形式,并对智能卡内的数据进行密封存储的方式进行保存,攻击者难以通过物理探测或软件探测盗取存储在智能卡上的密钥及用户ID信息[7-8]。另一方面,FPGA内部由大规模逻辑门阵列组成,要从中单独提取出密钥等敏感数据非常困难。此外,大部分FPGA已经具备对比特流及其内部结构的保护功能。因此,能够确保身份认证过程中所使用密钥及用户ID的静态安全性。

(2)在认证过程中,最有可能遭受到的攻击手段有冒充实体攻击、重放攻击、唯密文攻击。针对这些攻击,认证方案都具备相应的防范策略。

3.1 冒充实体攻击

假设攻击者盗取了用户的智能卡,为了获得智能卡上的ID信息,利用一个设备冒充合法的FPGA与智能卡连接。但由于在认证过程中,该冒充的设备无法成功地向智能卡证明其身份的合法性,使智能卡不会向该设备发送包含用户ID的相关信息,所以该安全封装结构能够抵抗“冒充实体攻击”。

3.2 重放攻击

假设攻击者截获了身份认证单元发送的认证信息cf′和cf,并对智能卡发动重发攻击。

(1) 在认证过程的步骤(3)中,智能卡产生一个新的随机数mu2,并用ef和nf对其进行加密,然后将加密后的结果cu2发给FPGA芯片中的身份认证单元。

(2) 攻击者将cf′发回给智能卡。

(3) 智能卡使用du和nu对cf′进行解密,得到mu,由于mu≠mu2,认证失败。

假设攻击者截获了智能卡发送的认证信息cu和cID,并对FPGA发动重发攻击:

(1) 在认证过程步骤(7)中,身份认证单元产生了一个新的随机数mf 2,并使用eu和nu对其进行加密,并将加密结果cf2传递给智能卡;

(2) 攻击者将cID发回给FPGA;

(3) 身份认证单元使用df和nf对cID进行解密,并将解密结果减去mu和mf2得到ID2;

(4) 身份认证单元使用SHA-1算法对ID2进行Hash运算,得到chash′;

(5) 由于chash′显然不能与ID Hash表寄存器中的值匹配成功,认证失败。

因此该安全封装结构能够抵抗“重放攻击”。

3.3 唯密文攻击

假设攻击者通过信道窃听截获了双方传递的所有认证信息,由于认证信息都是基于随机数产生的,所以每次传递的认证信息都不相同,这极大增加了攻击者分析密文的难度。而在认证过程的步骤(9)中,由于CID是通过对(ID+mu+mf)加密后得到,mu和mf都是随机数,所以每次认证的结果都不同,使攻击者也不能也通过分析CID获得用户ID的相关信息。

本文针对FPGA芯片内部功能单元的安全性问题,深入剖析了基于FPGA的安全封装结构,并对基于该结构的身份认证机制进行了重点研究,设计并实现了一种基于FPGA安全封装结构的身份认证模型。该模型采用基于公钥体制的双向认证机制,能够有效保证认证信息静态及动态的安全,从而达到确保安全封装结构有效性及芯片内部功能单元安全的目的。

责任编辑:gt

-

IMS终端AKA认证过程的研究与实现2010-04-23 2449

-

基于FPGA的身份认证智能卡设计2011-10-14 4993

-

如何设计FPGA加密认证系统?2019-08-05 2254

-

基于数字签名的双向用户认证方案double-directio2009-06-03 767

-

安全认证技术在“软件人”系统中的应用2009-06-20 751

-

无线局域网双向认证动态密钥管理方案2009-07-30 506

-

基于HARN改进算法的双向认证方案2009-08-04 624

-

基于改进的ELGamal签名的双向认证方案2009-08-24 1133

-

减少实现安全认证的步骤-中文版2013-10-10 652

-

RFID系统中基于CPK-ECC的双向认证协议2018-01-16 995

-

基于SHA-256安全认证工作原理的最新安全认证解决方案2018-03-16 6009

-

无线射频识别双向认证协议2018-03-06 951

-

基于区块链技术的高效跨域认证方案2018-03-29 1323

-

Altera功能安全锁步解决方案采用了FPGA、SoC,认证工具流程2018-08-31 1954

-

CPLD和FPGA中双向总线应该如何实现详细方法说明2019-06-11 1835

全部0条评论

快来发表一下你的评论吧 !