资料下载

×

如何使用FPGA实现节能型可升级异步FIFO

消耗积分:0 |

格式:rar |

大小:0.36 MB |

2021-02-02

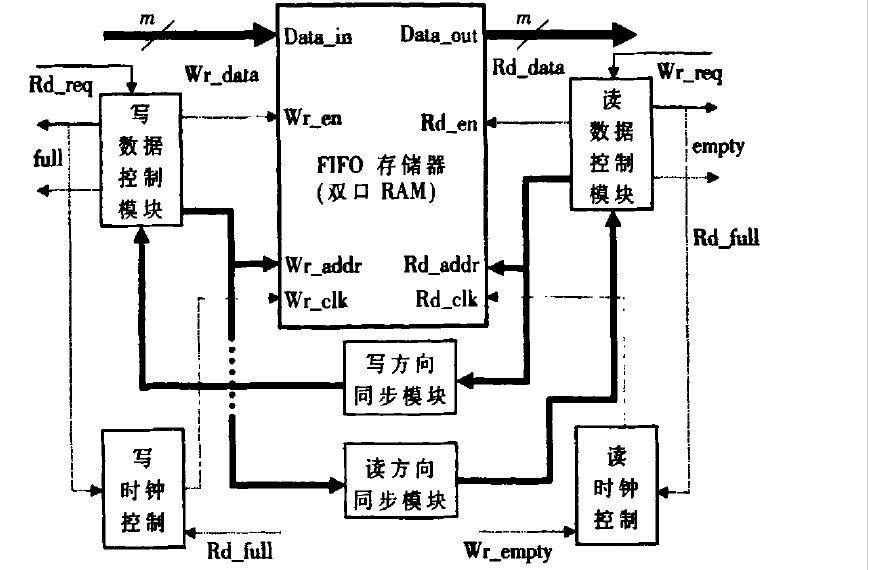

提出了一种节能并可升级的异步FIFO的FPGA实现。此系统结构利用FPGA内自身的资源控制时钟的暂停与恢复,实现了高能效、高工作频率的数据传输。该系统在Xilinx的VC4VSX55芯片中实现,实际可工作于高达100/153.6 MHz的读,写时钟域。本文所提出的结构不依赖于现有的IP核,基于此结构易建立可升级的IP核。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章