Verilog HDL语言中连续赋值的特征

电子说

描述

数据流模型化

本章讲述Verilog HDL语言中连续赋值的特征。连续赋值用于数据流行为建模;相反,过程赋值用于(下章的主题)顺序行为建模。组合逻辑电路的行为最好使用连续赋值语句建模。

7.1 连续赋值语句

连续赋值语句将值赋给线网(连续赋值不能为寄存器赋值),它的格式如下(简单形式):assignLHS_target = RHS_expression ;例如,wire [3:0] Z, Preset, Clear; // 线网说明assign Z = Preset & Clear; //连续赋值语句连续赋值的目标为 Z,表达式右端为“ Preset & Clear”。注意连续赋值语句中的关键词assign。连续赋值语句在什么时候执行呢 ?

只要在右端表达式的操作数上有事件 (事件为值的变化)发生时,表达式即被计算;如果结果值有变化,新结果就赋给左边的线网。在上面的例子中,如果 P re s e t或C l e a r变化,就计算右边的整个表达式。如果结果变化,那么结果即赋值到线网Z。连续赋值的目标类型如下:

1) 标量线网

2)。 向量线网

3) 向量的常数型位选择4) 向量的常数型部分选择5) 上述类型的任意的拼接运算结果下面是连续赋值语句的另一些例子:assgin BusErr = Parity| (One & OP) ;assign Z = ~ (A | B) & (C | D) & (E | F) ;只要A、B、C、D、E或F的值变化,最后一个连续赋值语句就执行。在这种情况下,计算右边整个表达式,并将结果赋给目标 Z。

在下一个例子中,目标是一个向量线网和一个标量线网的拼接结果。wireCout, C i n ;wire [3:0] Sum, A, B;。 。 .assign{Cout, Sum} = A + B + Cin;因为A和B是4位宽,加操作的结果最大能够产生 5位结果。左端表达式的长度指定为 5位(Cout 1位,Sum 4位)。

赋值语句因此促使右端表达式最右边的 4位的结果赋给S u m,第5位(进位位)赋给C o u t。下例说明如何在一个连续赋值语句中编写多个赋值方式。assgin M u x = (S = = 0)?

A : ‘bz, M u x = (S = = 1)?

B : ’bz, M u x = (S = = 2)?

C : ‘bz, M u x = (S = = 3)?

D : ’bz;这是下述4个独立的连续赋值语句的简化书写形式。

assign M u x = (S = = 0)? A : ‘bz;assign M u x = (S = = 1)? B : ’bz;assign M u x = (S = = 2)? C : ‘bz;assign M u x = (S = = 3)? D : ’bz;

7.2 举例

下例采用数据流方式描述1位全加器。

在本例中,有两个连续赋值语句。这些赋值语句是并发的,与其书写的顺序无关。只要连续赋值语句右端表达式中操作数的值变化 (即有事件发生), 连续赋值语句即被执行。如果 A变化,则两个连续赋值都被计算,即同时对右端表达式求值,并将结果赋给左端目标。

7.3 线网说明赋值

连续赋值可作为线网说明本身的一部分。这样的赋值被称为线网说明赋值。例如 :wire [3:0] S u m = 4‘b0;wire C l e a r = ’b1;wire A _ G T _ B = A 》 B, B_GT_A= B 》 A;线网说明赋值说明线网与连续赋值。说明线网然后编写连续赋值语句是一种方便的形式。参见下例。wire Clear;assign Clear= ‘b1;等价于线网声明e赋值:wire Clear= ’b1;不允许在同一个线网上出现多个线网说明赋值。如果多个赋值是必需的,则必须使用连续赋值语句。

7.4 时延

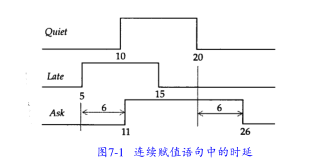

如果在连续赋值语句中没有定义时延,如前面的例子,则右端表达式的值立即赋给左端表达式, 时延为0。如下例所示显式定义连续赋值的时延。assign #6 Ask = Quiet | | L a t e;规定右边表达式结果的计算到其赋给左边目标需经过 6个时间单位时延。例如,如果在时刻5,L a t e值发生变化,则赋值的右端表达式被计算,并且 A s k在时刻11( = 5 +6)被赋于新值。图7 - 1举例说明了时延概念。

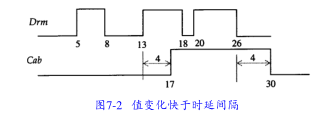

如果右端在传输给左端之前变化,会发生什么呢?在这种情况下,应用最新的变化值。下例显示了这种行为:assign #4 Cab = Drm;图7 - 2显示了这种变化的效果。右端发生在时延间隔内的变化被滤掉。例如,在时刻 5,Dr m的上升边沿预定在时刻9显示在Cab上,但是因为Drm在时刻8下降为0,预定在Cab上的值被删除。同样, Drm在时刻1 8和2 0之间的脉冲被滤掉。这也同样适用于惯性时延行为:即右端值变化在能够传播到左端前必须至少保持时延间隔;如果在时延间隔内右端值变化,则前面的值不能传输到输出。

对于每个时延定义,总共能够指定三类时延值:1) 上升时延2) 下降时延3) 关闭时延这三类时延的语法如下:

在第一个赋值语句中,上升时延、下降时延、截止时延和传递到 x的时延相同,都为 4。在第二个语句中,上升时延为4,下降时延为8,传递到x和z的时延相同,是4和8中的最小值,即4。在第3个赋值中,上升时延为 4,下降时延为8,截止时延为6,传递到x的时延为4 ( 4、8和6中的最小值)。在最后的语句中,所有的时延都为 0。上升时延对于向量线网目标意味着什么呢 ? 如果右端从非0向量变化到0向量,那么就使用下降时延。如果右端值到达z,那么使用下降时延;否则使用上升时延。

7.5 线网时延

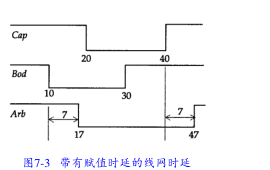

时延也可以在线网说明中定义,如下面的说明。wire #5 A r b;这个时延表明A r b驱动源值改变与线网A r b本身间的时延。考虑下面对线网 A r b的连续赋值语句:

assign # 2 Arb = Bod & Cap;

假定在时刻1 0,B o d上的事件促使右端表达式计算。如果结果不同,则在 2个时间单位后赋值给 A r b,即时刻1 2。但是因为定义了线网时延,实际对 A r b的赋值发生在时刻17( = 10 + 2 + 5)。图7 - 3的波形举例说明了不同的时延。图7 - 4很好地描述了线网时延的效果。首先使用赋值时延,然后增加任意线网时延。如果时延在线网说明赋值中出现,那么时延不是线网时延,而是赋值时延。下面是 A的线网说明赋值,2个时间单位是赋值时延,而不是线网时延。w i r e #2 A = B - C; // 赋值时延

7.6 举例

7.6.1 主从触发器

下面是图5 - 9所示的主从触发器的Verilog HDL模型。

7.6.2 数值比较器

下面是8位(参数定义的)数值比较器数据流模型。

原文标题:Verilog入门-数据流模型化

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

阻塞赋值与非阻塞赋值2023-09-12 2024

-

C语言中赋值运算符详解2023-08-18 2997

-

Verilog语言中阻塞和非阻塞赋值的不同2021-08-17 7340

-

Verilog HDL语言中任务与函数的比较2021-07-02 3156

-

Verilog HDL语言技术要点2020-09-01 5467

-

VerilogHDL语言连续赋值与过程赋值方式如何区分2020-07-20 7149

-

Verilog HDL语言中的分支语句2019-11-20 6473

-

基于FPGA Verilog-HDL语言的串口设计2017-02-16 1393

-

【锆石科技】关于 Verilog HDL 语言的一些关键问题解惑【免费下载】2016-08-17 51619

-

Verilog HDL硬件描述语言_Verilog语言要素2016-04-25 848

-

炼狱传奇-赋值语句之战2015-03-22 3282

-

Verilog HDL语言简介2010-02-09 4189

-

Verilog HDL语言实现时序逻辑电路2010-02-08 5181

-

基于Verilog HDL语言的FPGA设计2009-08-21 699

全部0条评论

快来发表一下你的评论吧 !