介绍极限参数-ID & EAS依Hunteck 100V 5mΩ DFN5*6 MOSFET为例子

功率器件

描述

作者: Hunteck Sen Chen

小编在过去拜访客户最被经常问到的问题,第一个:为什麽MOS规格上面103A(依050N10为例子),为什麽我输出电流才5~6A不到,为什麽MOS都已经烫到不行。第二个:为什麽我原本用A家公司的MOS,但为什麽换你们家MOS一下子就烧掉了是不是Eas太小了?

首先回答第一个问题,所有MOS规格书上面的ID是一个有明确边界条件规定下的理论数值。因为在应用中可能会有各种各样的散热条件。作为MOS厂商出具的规格书,不可能把千差万别的散热条件都都考虑进去。所以在MOS的规格书上面会给出最好和最差散热条件下的热阻,这样就可以让客户清楚的指导温升的范围和极限在哪里。

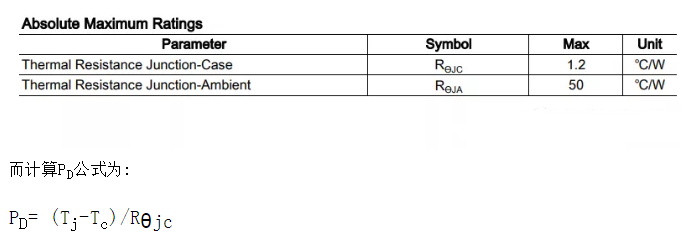

这里就要引入两个概念就是RθJC和RθJA。

RθJC是芯片到芯片背面的散热片的热阻。

RθJA 是MOS焊接在一块1平方英寸的1盎司PCB上的时候,芯片到外接环境的热阻。

(如果是背面么有散热的封装形式比如SO8封装还会引入一个替代概念叫RθJL

RθJL是芯片到芯片管脚的热阻的热阻。)

这颗Tj MOS結溫为150℃,而Tc=25℃,那我們就算出來了PD为104.1666W,故这颗MOS最大所承受功耗为104W(050N10规格书有写)那我们有了功率数值后,而MOS的Rds都是已知的数值,只是我们还要知道的另外一件事情MOS的Rds为正温度系数,并且我们在一般RDSmax都是在Tc=25℃都量测的(如下表),所以要知道高温测试下的电流就是要把RDS做一个温度系数补偿,我们把温度系数在公式中我们习惯取为K。(如下曲线图表示)

那我們算一下 Tc= 100℃ 狀況下,ID多少?

ID=((150-100)/(5m*1.2*2))^0.5 (K值由曲線接近2 取2即可另外RθJC都採max值)

ID=64.544, 故050N10規格为65A。

同理 Tc= 25℃ 狀況下,ID计算出來為102.06,故050N10 規格为103A。

极限参数介绍:

ID最大漏源电流。是指场效应管正常工作时,漏源间所允许通过的最大电流。场效应管的工作电流不应超过 ID 。(此参数会随结温度的上升而有所减额)

PD最大耗散功率。是指场效应管性能不变坏时所允许的最大漏源耗散功率。

Tj最大工作结温。通常为 150 ℃ 或 175 ℃ ,器件设计的工作条件下须确应避免超过这个温度,并留有一定裕量。

Tc 周围环境温度。

RθJC结点到周围环境的热阻

*这里需要特别注意的是,在上面的计算中用到的是RθJC这个热阻。默认的是散热片的温度永远是25℃。也就是说,这个计算中默认的是散热片的散热效率是无穷大,无论多少热量都不能改变散热片的温度25℃。这是PD的理论最大值。客户使用的散热片越大,或者使用风冷或者水冷,MOS的PD值就会无限的接近这个值。有背面散热的MOS,客户可以有很多手段去给MOS散热,所以大家约定俗称,在规格书中给出的PD和ID是接近理论的最大值的。

那PD的最小值又是什么呢?

可以用RθJA再来计算一下。我们默认客户用的PCB都会大于1平方英寸。这样得出的PD= (Tj-Tc )/ RθJA为:2.496W。这个是理论的最小值。

所以在一些没有背面散热的封装的MOS规格书上,比如SOIC8,即使同样的内阻的MOS,会给出小很多的ID和PD值,就是因为这些MOS可以散热的手段很有限,所以大家约定俗称,在规格书中给出的PD和ID是接近理论的最小值的。

其次第二个问题:造成MOS烧毁因素(过流、过压、静电)很多,所以光靠一个现象来判断MOS烧毁原因是不够的,此篇先针对EAS做一个介绍。

EAS:单次脉冲雪崩击穿能量,而业界做EAS最普通的测试方式就是UIS:英文全称为Unclamped Inductive switching,中文译为非嵌位感性负载开关过程。UIS测试实质上就是一种模拟 MOS器件在系统应用中遭遇极端电热应力的测试,通过这种测试,我们可以得到MOS器件反向雪崩时耐受能量的能力。而下图就是UIS基本测试电路及波形,因此有电感的存在,当MOS ON回路时,储存在电感中的能量必须在关断瞬间全部释放,此时MOS上同时经过高电压和大电流,故我们反覆提升ID的上限就可以知道MOS 最大可承受的能量。

*这裡因为是介绍中低压MOS故取这公式及此UIS测试方式

因此举例050N10 UIS测试下,其波形如下图:(CH1 Vgs CH2 VDS CH3 ID)

所以EAS=0.5*79.2^2*0.1m=313mJ,但由于考虑Any users对EAS要求不同,故规格书写80mJ把安全馀量留了下来。

恆泰柯目前SGT 在100V 4~5m ohm左右产品,EAS优于业界水准,是因为先进SGT MOS工艺复杂,要考虑cell间的平衡问题、震荡问题、epi中的极限电场强度及寄生二极等参数,想要克服这些问题需要大量的技术经验与市场验证,恰好这就是恆泰柯优势。

*小编来科普一下:MOS在製造过程会在内部形成一个寄生三极管,只不过B和E极是短路在一起的,所以在正常情况下不会激发,视同为二极管。只有在有些UIS打死的时候才会激发出来,一旦激发出来MOS就很容易死,因此有些资料会直接说UIS容易打死寄生二极管此说法。而目前柯泰科在寄生二极管的Rp和Rc都优化到了极致,故寄生二极管的UIS问题并不是瓶颈。

那有小伙伴可能会问UIS测不过会是什麽的波形呢。小编也用050N10的波形来做说明如下图。(大部份会是这波形,但也会例外MOS毕竟已经Fail,MOS内部参数会让波形产生不规则情况)

斜率1:给电感充电,di/dt=Vdd/L,Vdd是UIS测试机加的电压 (L就是UIS试验用的电感)

斜率2:电感放电,MOS雪崩,di/dt=BVDSS/L, BVDSS是 UIS时MOS的雪崩电压

斜率3:MOS失效,DS短路,di/dt=Vf/L, Vf是MOS 失效后,包括电感寄生电阻,MOS失效后的电阻,等所有回路中电阻和续流二极管上的压降的总和。

*另外有些客户经常会问,恒泰柯的SGT晶圆面积会比普通的trench MOS 小很多,是不是EAS的能力就会相应的小很多呢?这里忽略了一个更重要的因素就是:温度是不同的。在UIS的时候,热是在us时间量级产生的,这么短的时间,能量只能由芯片表层的MOS结构来吸收。SGT的MOS结构的深度是trench的4-7倍,即使芯片面积小一倍,能够吸收热量的Si的体积也是trenchMOS的数倍。这样就会使同样电流密度UIS的时候,SGT的MOS结构温度更低。在相同的提二极管的情况下,温度更低,承受的UIS电流密度就会按照温度的指数增加。所以SGT的理论UIS 电流肯定比trench MOS 高。现实中很多时候确实会发生SGT更容易在电路中过压打死。原因是因为SGT更快,trench慢很多。更快的SGT可以为客户节省开关损耗,但是客户要相应的吧PCB layout画得更加紧凑,变压器的漏感更小。不然的话,SGT更快所产生的的更高的应力使得SGT需要承受的UIS电流密度是trench的几倍甚至10几倍。所以把应力降下来才是王道。

除此之外,各家MOS原厂在描述EAS值往往都是不同测试条件进行,故用各家的最终数值来对比是不对的,如果真的要比就只能在做一个测试条件来做判断才有意义,而相较于ID我们就可以依规格书上面的数值来进行各家厂家一个初步评估,看谁的最大漏源电流及最大耗散功率是最适合被选择使用产品最能合适。

最后小编介绍ID & EAS完后,接下来的日子也会介绍其他参数。

-

onsemi LV/MV MOSFET 产品介绍 & 行业应用2024-10-13 1666

-

AOS推出新款100V MOSFET AONA669162024-01-26 3440

-

MOS管的ID与极限参数介绍2023-04-03 1079

-

N 沟道 100V 8.5 mΩ 标准电平 MOSFET,采用 TO220F(SOT186A)-PSMN8R5-100XS2023-03-03 524

-

宝砾微MOS管 PL0807N10 DFN5*6 100V/74.4A N沟道MOSFET2023-03-02 1816

-

N 沟道 100V,5.6 mΩ 标准电平 MOSFET,采用 TO220-PSMN5R6-100PS2023-02-23 624

-

N 沟道 100V,5 mΩ 标准电平 MOSFET,采用 TO-220-PSMN5R0-100PS2023-02-22 464

-

采用 LFPAK56 封装的 NextPower 100V、10.9mΩN沟道 MOSFET-PSMN011-100YSF2023-02-20 606

-

加湿器100V耐压MOS管TO-252 100V低结电容5A2020-09-23 1046

-

SL30150/30V 150A 1.9毫欧的N沟道场效应管,DFN5*6A-8 EP封装2020-05-29 1329

-

针对快充应用设计3 mΩ、5 mΩ、10 mΩ,DFN33和DFN56封装的MOSFET2018-06-15 2752

-

Diodes 100V MOSFET H桥采用5mm x 4.5mm封装有效节省占位面积2016-02-16 1925

全部0条评论

快来发表一下你的评论吧 !