如何使用Verilog HDL描述可综合电路?

电子说

描述

1、如何使用Verilog HDL描述可综合电路

Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬件电路的文本描述。所以编写前:

对所需实现的硬件电路“胸有成竹”;

牢记可综合Verilog HDL与电路结构一一对应的关系;

确认电路指标是什么:性能?面积?

硬件思维方式,代码不再是一行行的代码而是一块一块的硬件模块;

达到以上几点,就可以确保写出行云流水般的高质量代码。

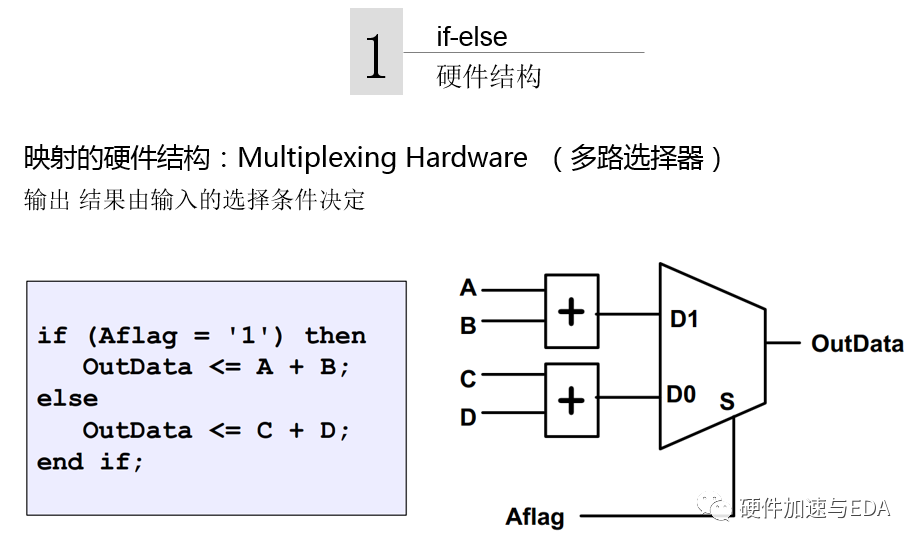

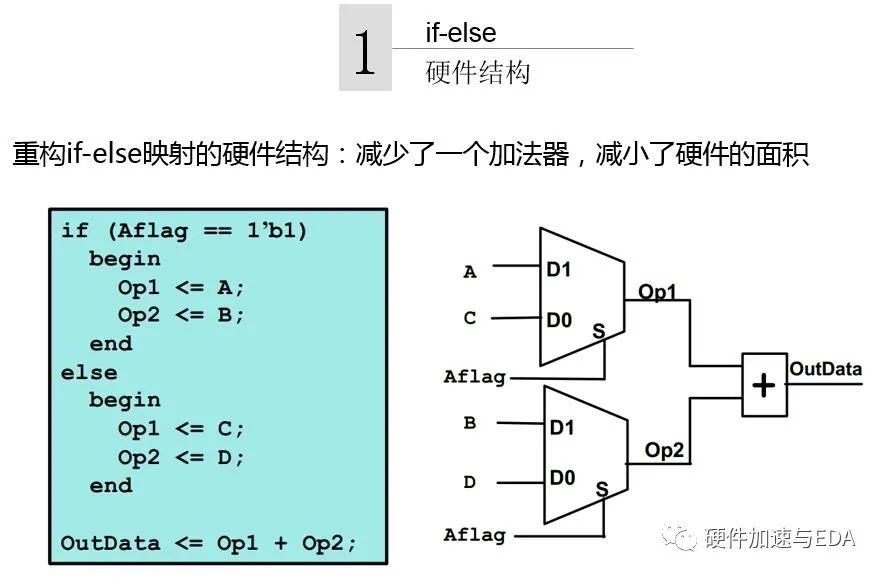

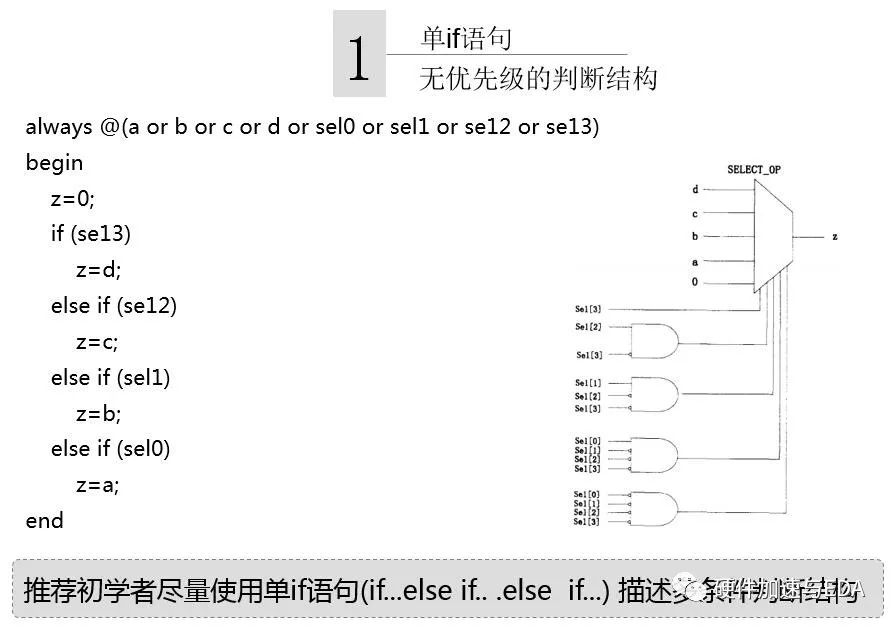

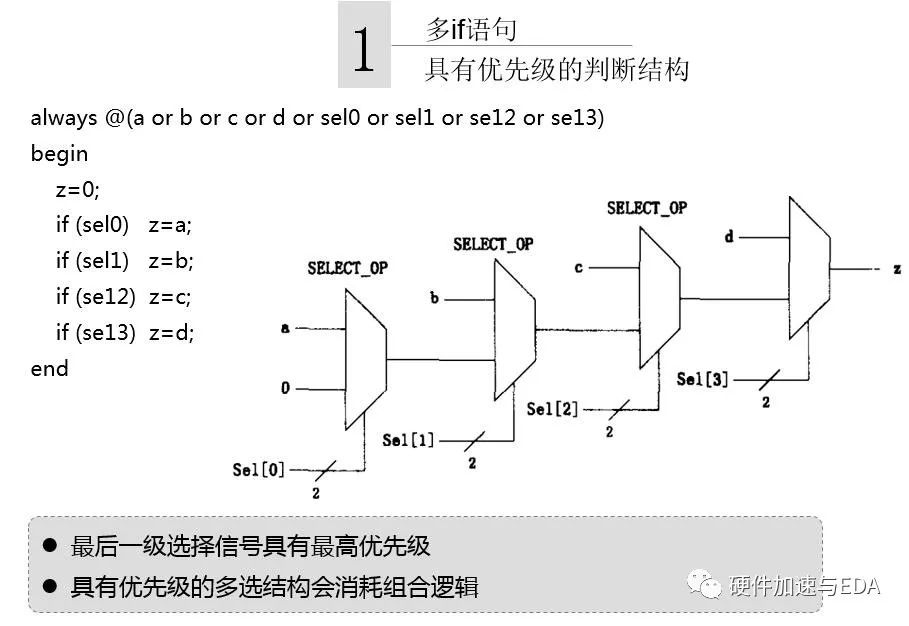

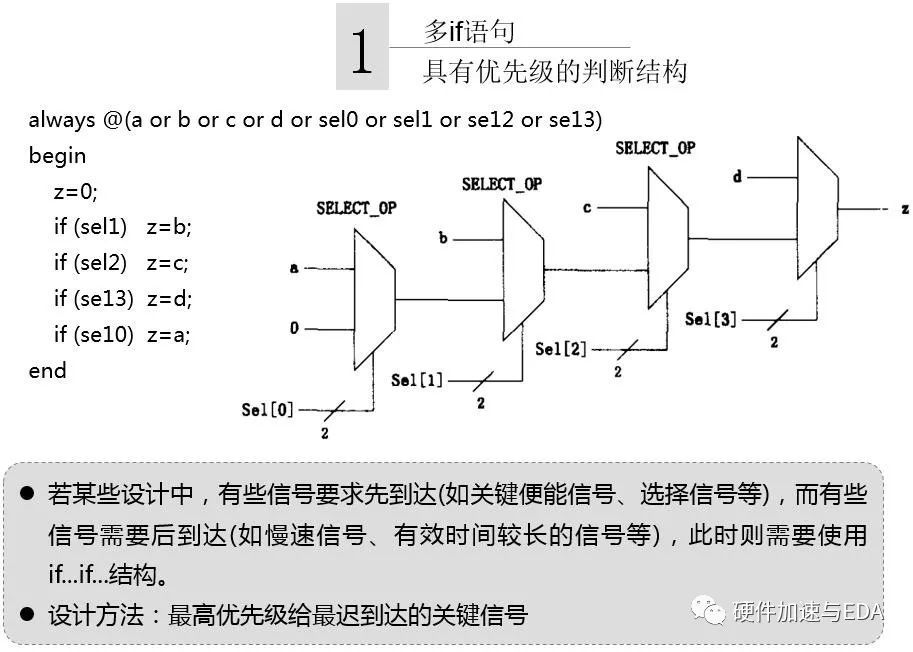

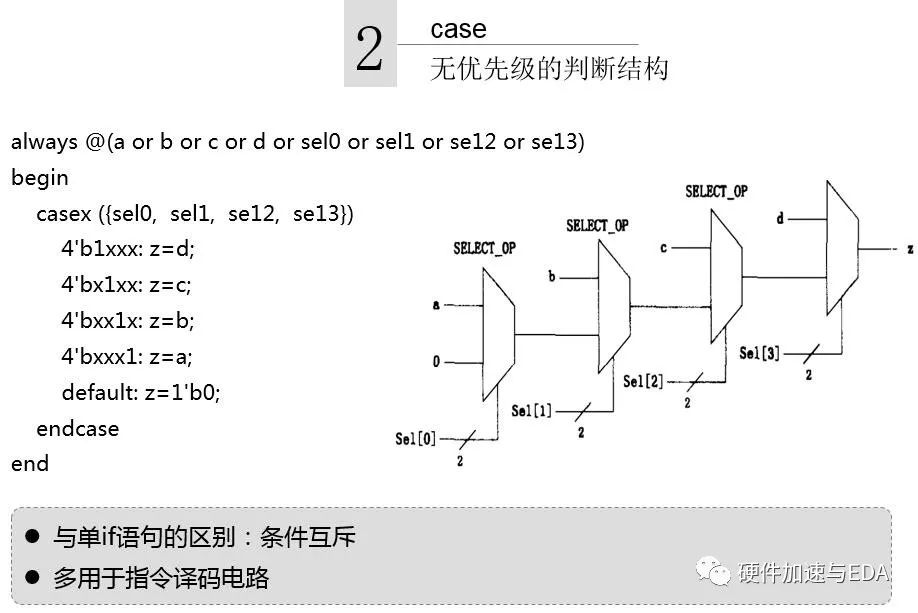

关于代码与硬件电路的对应关系,参见如下图片,引用自Synopsys官方文档:

2、自动化生成代码

如果一定要有奇淫技巧的话,那么代码自动化生成技术就一定可以配得上这个称号。

近十年来,数字集成电路规模和复杂度飞速提高。这给数字集成电路工程师带来了不仅是脑力上的劳动的增加,更多是体力重复性工作的增多。传统的手工代码的编写存在很多弊端:

对于模块的代码工程师,要面对许多设计文件。而这些文件之间可能相互不一致,给代码的编写带来了很多的困扰。

代码工程师需要将这些文件中的很多设计信息体现在代码中,其中一些信息是充分性的誊写。这不仅带来了很多枯燥复杂的工作量而且人工参与过多也容易引入很多粗心带来的错误。

由于各个模块连接信号之多导致信号文件的手写工作量很大。每个信号文件小则几千行大则上万行信息。而且一旦有信号连接的变动需要相应修改多个模块的信号文件。

如果设计文件改动相应的设计文件很容易出现哪几处忘记改动的问题。

而脚本语言又有着强大的处理文本的能力。将脚本语言应用于数字电路设计中,作为设计文档和EDA工具的黏合剂,能够大大增加设计的速度。具体方法为:使用脚本语言从设计文档中提取有用的信息来生成想要的Verilog HDL代码,从而大大减少了IC设计者的工作量,并提高了代码的质量。

其好处有:

很好的设计一致性:保证了设计概念一旦变动即设计文档稍加修改,对应的VHDL代码就会相应的改变,不需要工程师手动改变代码。

兼容性强:该自动生成代码工具中设置了一个配置文件,供设计工程师的配置修改。对于不同的项目,通过修改配置该文件可以直接是代码相应变化,有一定的灵活性。此外,该自动生成代码工具已经应用于两个以上项目中,实践证明有很好的兼容性。

代码维护方便:对于设计代码的更新或升级,只需要从新运行下该工具即可,不需要一点点该写代码。

使用简单:集成大量脚本,使用工具时只需要运行一条命令即可。

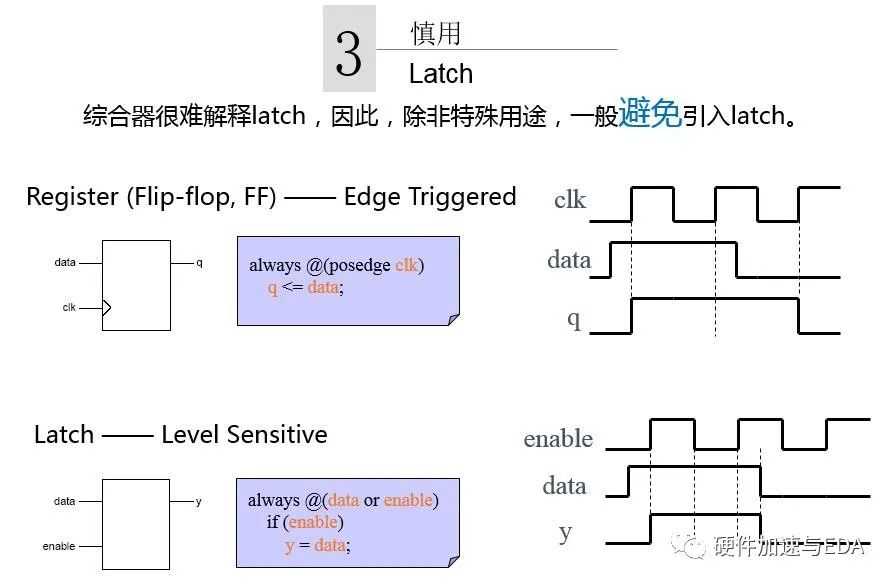

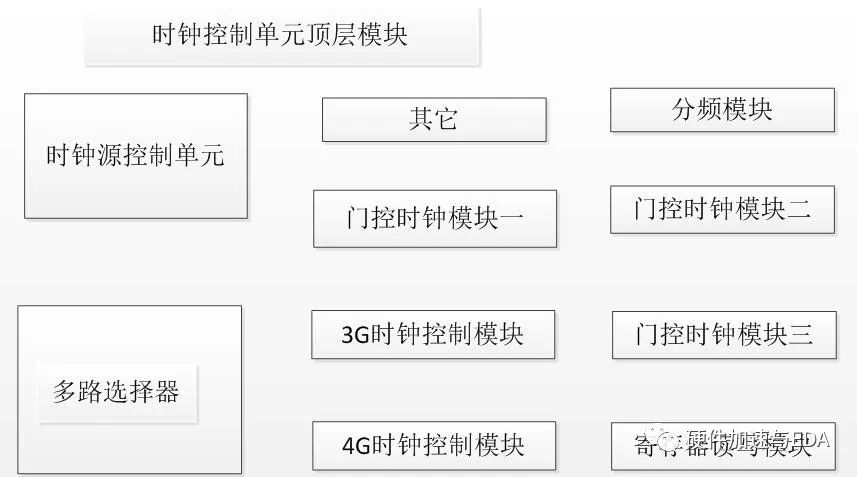

本文将举一个Perl语言在代码自动生成中的应用实例,下图为一款SoC芯片中全芯片的时钟控制电路框图:

时钟控制模块实现配置PLL参数、选择输出时钟源、时钟分频、时钟门控、bank切换、输出时钟等功能。3G、4G是系统通讯单元,向时钟控制单元申请时钟。PLLs是时钟源,是时钟控制单元的输入。时钟控制单元有七大主要模块,分别为时钟源控制模块、bank切换模块、分频模块、时钟门控模块、多路选择器模块、寄存器、3G4G时钟握手模块。时钟源控制模块控制时钟源的大小、开关。bank切换模块使时钟控制单元能正常工作在不同的电压下。

时钟控制单元的的工作机理如下:首先,外部模块向时钟控制单元请求时钟,并修改并写寄存器状态;时钟源控制单元根据寄存器中的内容配置时钟源Plls,并提供了所有的时钟源。然后,分频器完成这些时钟源预分频的操作,并将其作为多路选择器的时钟源。而多路选择器则从输入的时钟源中选择输出主时钟。主时钟通过分频模块产生所有的分频使能信号,这个过程中,需根据寄存器所配置的分频数来输出不同的频率的时钟。同时,根据系统的实时需求,通过由SPCU控制的bank选择器完成门控时钟的实现,降低系统的功耗。

以上是时钟控制模块的功能分析,那么如何通过代码自动生成技术来实现呢?

(1)首先,我们把这些模块梳理下,形成一个自顶向下的层次结构,如下图。如图中所示,顶层模块完成对底层模块的连接,底层模块实现时钟控制单元的功能。

针对代码自动生成问题,对于顶层模块来说,承担的功能是自动地将底层数十个模块连接起来。对于底层模块来说,需要根据不同的功能定制需求,来自动化地生成所有功能性的代码,然后被顶层调用和连接。这样的话,就存在两个问题:[1]自动生成顶层模块?[2]自动生成底层模块?

(2)顶层模块:通常来说,对于一个复杂的SoC芯片,会有万数量级的信号需要进行匹配和连接。而能够自动生成的信号文件中的信号连接有两个特点:一是信号命令规律性强二是信号的连接关系可以从设计文件中体现。满足了这两点,便可以实现信号文件的自动化。

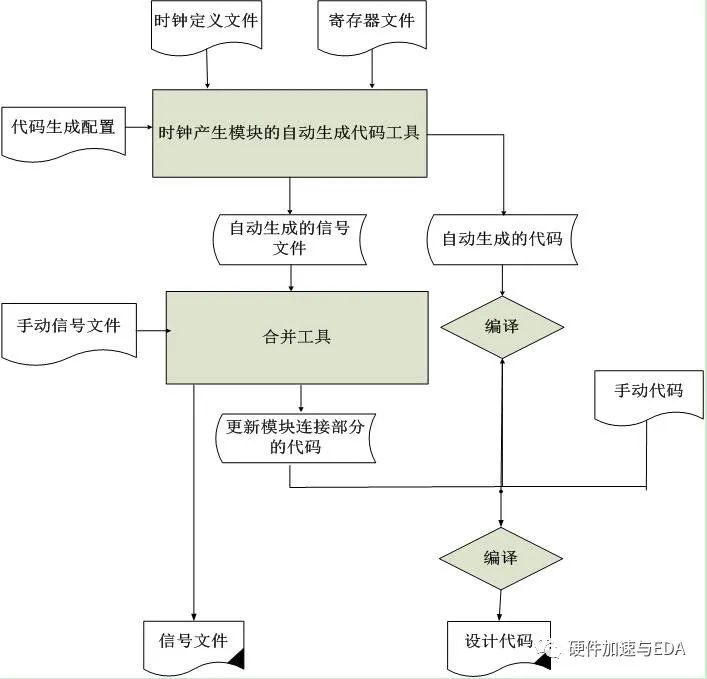

(3)底层模块此处即可体现Perl脚本强大的数据处理功能,针对该问题,将脚本划分为三类:提取脚本、生成脚本和集成脚本三种。提取脚本用来从输入文件中提取有用的设计信息到存储单元中;生成脚本从存储单元获得有用信息来生成各个功能模块的代码;集成脚本将所有的脚本集成在一个脚本里,方便统一化使用。以下是代码生成的脚本流程图:

如图所示,输入的文件都是excel和文本形式,Perl脚本首先读取技术文档,从中解析出时钟模块所需的连接、频率、时钟域等信息,基于此信息建立一个数据库。然后,根据实际芯片的具体需求,即配置文件,生成相应的自动化控制模式和需求。最终,依据配置文件和数据库,完成所有所需verilog代码的生成。需要注意的是,并不是所有的代码都可以自动生成,有些结构特殊的电路,只能通过手工编写来完成。所以,自动编写通常完成较为规整的、有规律性的代码,手工书写作为补充。这样即可保证得到高质量的代码。

总结

Perl语言强大的正则和hash能力成就了代码自动生成技术,在这个领域,其他脚本语言黯然失色。当然,使用Python也可以同样的功能。

但是,这还远远不够智能。

短期内,如何使得代码生成技术更加友好,更方便移植和管理?如何更加彻底地剥离人工干预的工作,脚本自动决定哪些电路需要自动生成的代码?

在更远的未来,是否能够抛弃掉太纠结于细节的Verilog语言?高级语言综合技术HLS、Chisel、AI自动生成代码和电路是否是更好的选择?

原文标题:书写Verilog 有什么奇技淫巧

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

二十进制编码器及Verilog HDL描述 Verilog HDL程序的基本结构及特点2023-08-28 5643

-

一本Verilog HDL代码对应电路的书,助你快速编写可综合模型2023-05-26 2421

-

Verilog HDL verilog hdl和vhdl的区别2021-07-23 12311

-

Verilog教程之Verilog HDL程序设计语句和描述方式2020-12-09 1349

-

设计与验证:Verilog HDL(清晰PDF)2016-10-10 6540

-

Verilog HDL硬件描述语言_门电平模型化2016-04-25 836

-

Verilog HDL硬件描述语言2015-12-29 737

-

verilog HDL 可综合模型的结构2012-10-20 2759

-

Verilog_HDL的基本语法详解(夏宇闻版)2012-10-08 2198

-

HDL的可综合设计简介2012-01-17 1429

-

Verilog HDL代码描述对状态机综合的研究2011-12-24 770

-

Verilog HDL语言简介2010-02-09 4193

-

Verilog HDL程序基本结构与程序入门2010-02-08 2634

-

Verilog HDL综合实用教程2009-07-20 824

全部0条评论

快来发表一下你的评论吧 !