怎样实现高效的芯片与封装的联合仿真?

描述

随着5G技术的发展,射频前端(RFFE)设计变得越来越复杂,而系统级封装(SiP)技术因其可集成多颗裸芯片与无源器件的特点,开始被广泛用于射频前端的设计中。 芯片设计与封装设计传统上是由各自工程团队独立完成,这样做的缺陷是增加了迭代时间和沟通成本。如果能够实现芯片和封装协同设计,不仅可大幅减少迭代次数,提高设计成功率,而且使能芯片工程师在设计流程中随时评估封装性能。 目前在市场上,要实现快速的芯片和封装协同仿真的方法并不多。芯和半导体独创的这套联合仿真流程中,三维建模简单易用,并配有专门针对联合仿真的优化求解器,能够提供更高的仿真加速和仿真效率。

三维建模和仿真流程

1.导入芯片和封装版图文件

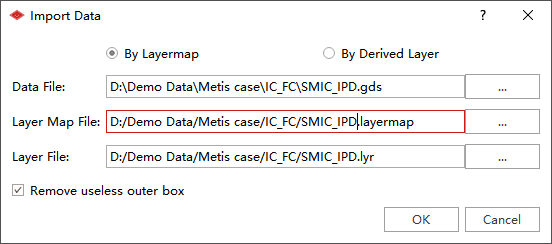

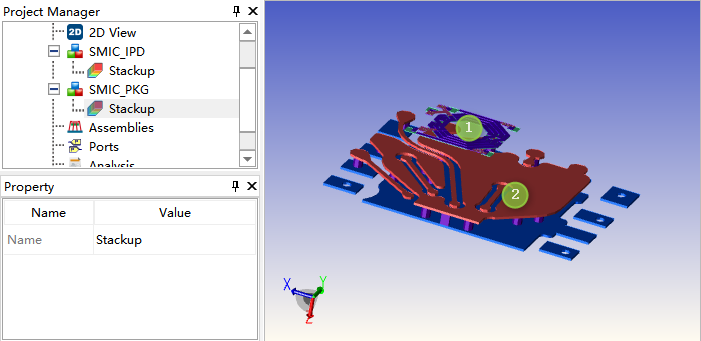

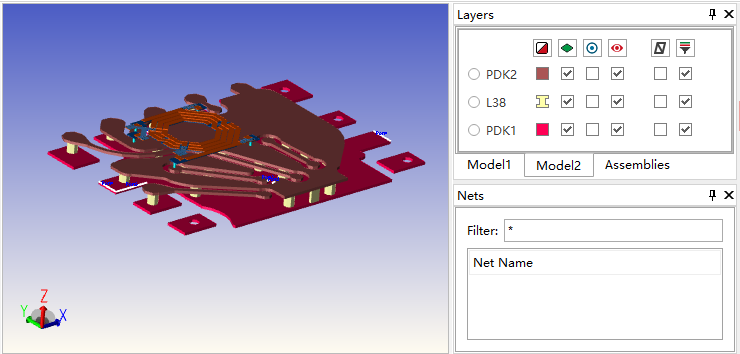

在Metis工具中,可直接导入Cadence的设计文件(.mcm/.sip/.brd)、ODB++文件、以及DXF和GDS文件。本案例中芯片和封装版图均为GDS格式,同时还需要layermap文件和仿真工艺信息lyr文件。依次导入芯片和封装版图后,在Metis 3D视图中自动生成了它们的三维结构(图2),此时它们的相对位置是任意,需要通过Bump将它们连接在一起。

图1 导入版图界面

图2 导入芯片和封装文件

2.模型堆叠

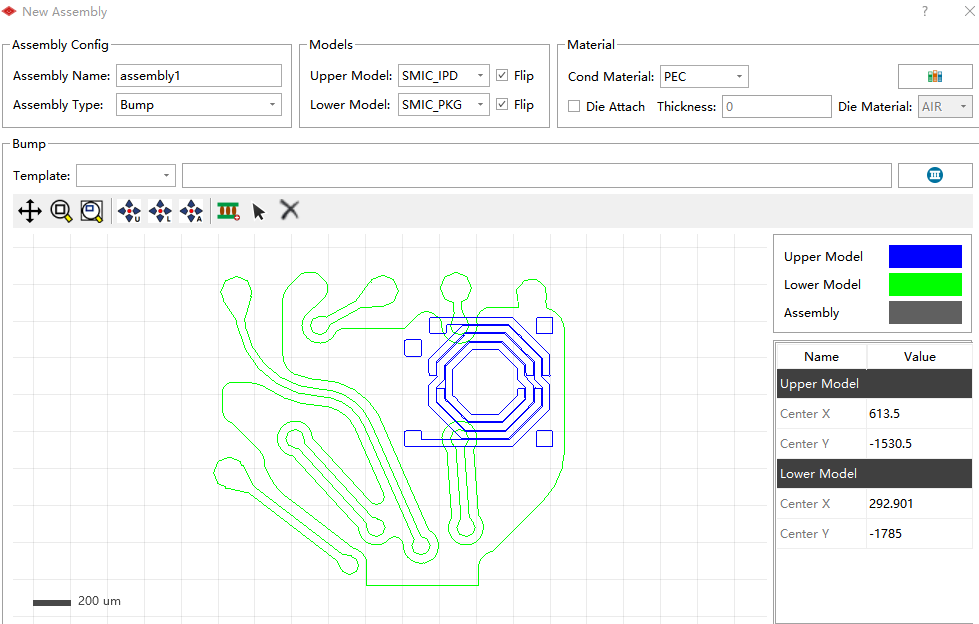

在左侧的项目管理栏,选择Assemblies,进入堆叠设置界面。在上侧Model栏,我们将芯片设置为Upper Model,将封装设置为Lower Model(图3)。

图3 切割后的模型 左:Serdes; 右:DDR

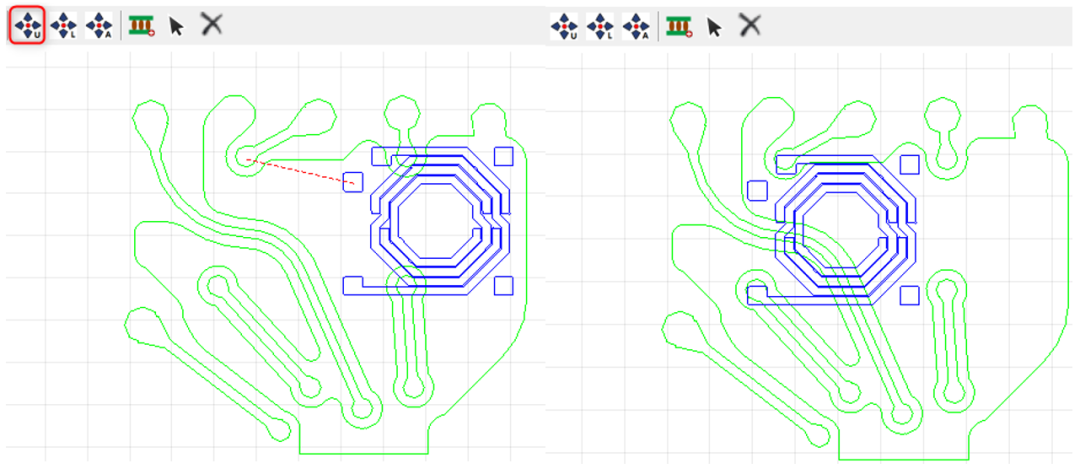

接着我们使用拖拽功能,将Upper Model拖拽至正确的封装焊点位置(图4)。

图4 移动upper Model至正确位置(右图)

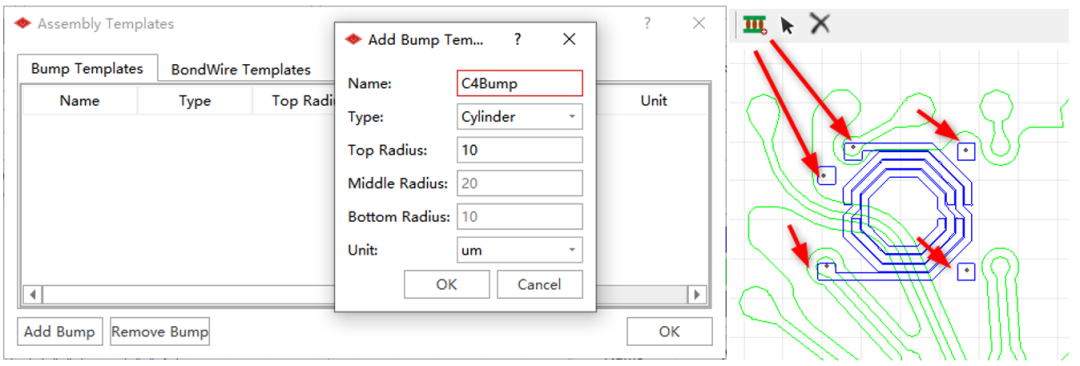

最后创建合适的Bump模型,通过在芯片pad上点击增加Bump模型,将芯片和封装结构连接在一起(图5)。

图5 Bump建模及添加

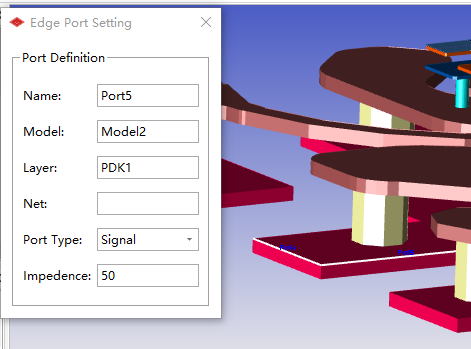

3.端口添加

模型堆叠完毕后,用户可以直接在3D视图中添加集总端口,其中信号类型,金属层次,端口阻抗可任意配置。在本案例中,我们选择封装焊盘的一边作为信号端口。

图6 叠层及端口管理

图7 生成的最终仿真模型

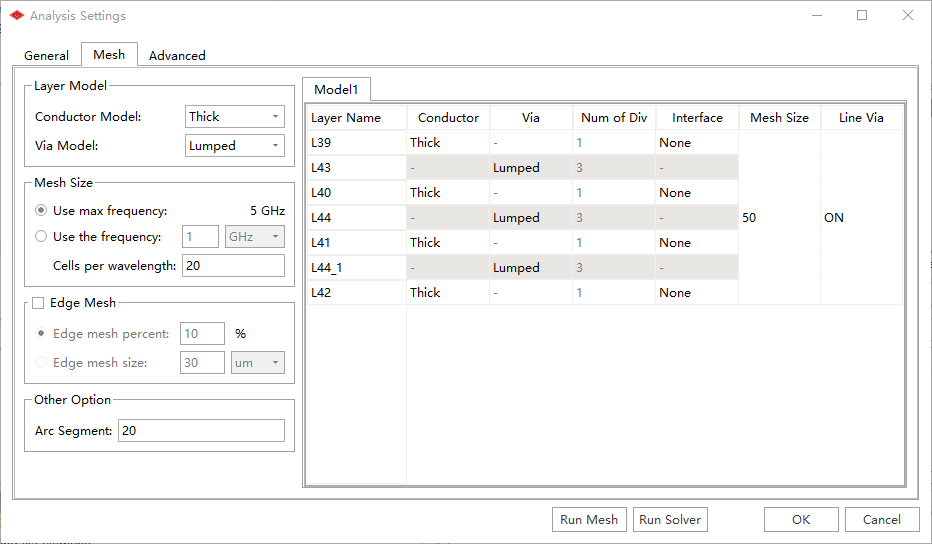

4.仿真环境设置

Metis的网格划分、金属和过孔模型可以根据不同的结构进行分开设置,从而达到仿真精度与效率的双重提升。本案例中芯片的金属设置为Thick,过孔为Lumped,网格大小为50um,而封装的金属设置为3D,过孔为3D,网格大小为200um。最后点击Run Solver进行联合仿真。

图8 芯片的仿真设置

5.仿真结果比对

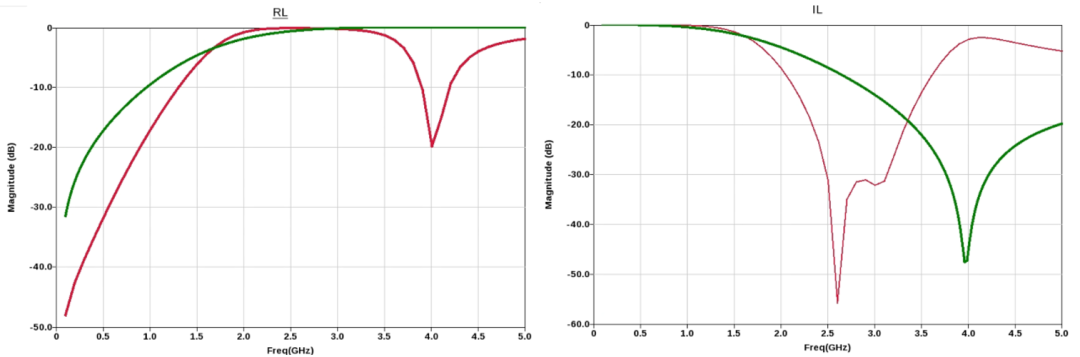

我们分别仿真了不带封装和带封装两种应用场景,来分析封装对芯片滤波特性的影响。绿色曲线是不带封装的芯片仿真数据,红色曲线是带封装的芯片仿真数据。通过对比RL和IL两个指标,我们发现在通带内滤波器特性并没有明显恶化,但是由于封装的容性寄生,导致带外的抑制性能急剧下降。这将对射频系统接收信号和本征信号带来干扰,从而导致信号的阻塞。由此我们得出结论,封装效应是芯片设计不得不考虑的重要因素,同时Metis能很好的解决联合仿真建模困难,优化设计效率低的问题。

图9 RL与IL比对结果

总结

本文介绍了一种采用芯和半导体的Metis工具实现芯片和封装联合仿真的方法。通过Metis分别导入芯片和封装的版图文件,将芯片倒装焊在封装基板上,建立三维堆叠模型。最后使用Metis进行快速的电磁仿真分析,我们考察了封装对芯片性能指标的影响。此案例可以帮助设计人员进行芯片和封装协同设计可大幅减少迭代次数,提高设计成功率,使能芯片工程师在设计流程中随时评估封装性能。

编辑:jq

-

在PSIM中进行VHDL的联合仿真2023-05-23 5680

-

怎样实现 “高效的芯片与封装的联合仿真”?2022-02-08 543

-

nanosim和vcs混合仿真的过程是怎样的?2021-06-18 2934

-

modelsim联合仿真不成功2019-05-16 2457

-

Maxwell与Simplorer联合仿真2017-11-17 5392

-

labview与simulink联合仿真2017-03-18 4526

-

芯片的fpga实现及仿真2016-01-20 1013

-

基于labview和matlab的联合仿真之一官方例程的实现2015-09-05 100251

-

MPLAB X IDE 和 Proteus 8 如何实现联合仿真?2015-07-21 8838

-

labview与solidworks联合仿真2014-04-10 5927

-

怎样使用labview2012和multisim进行电路实验联合仿真!2014-04-09 3085

-

怎样实现orcad+padslogic+padslayout的联合同步?2013-10-23 9883

-

寻找ansoft与matlab的联合仿真2012-05-03 4339

全部0条评论

快来发表一下你的评论吧 !