简述锁相环技术

描述

1 锁相环的基本概念

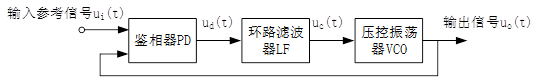

锁相环(Phase Locked Loop,PLL)是一个闭环负反馈相位控制系统,至少包含3个基本单元电路:

鉴相器(Phase Detector,PD);

环路滤波器(Loop Filter,LF);

压控振荡器(Voltage ControlledOscillator,VCO)。

锁相环框图

2 锁相环的基本单元电路

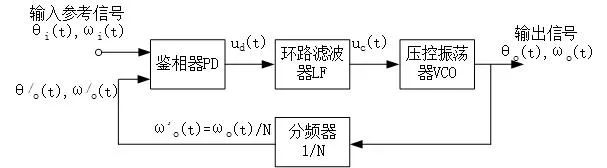

加入分频器的锁相环由鉴相器(Phase Detector,PD)、环路低通滤波器(Loop Filter,LF)、压控振荡器(Voltage Controlled Oscillator,VCO)和分频器(Frequency Divider)组成。输入信号的相位和频率分别为θi(t)和ωi(t),单位分别为rad和rad/s;输出信号的相位和频率分别为θo(t)和ωo(t),单位分别为rad和rad/s。

锁相环框图

鉴相器将输入周期信号的相位与压控振荡器输出信号的相位进行比较,得到相位差θc,PD将θc转换为误差电压信号ud(t)输出。误差电压通过环路滤波器进行滤波,滤除交流成分,滤波的过程即为对误差电压信号ud(t)求平均值的过程,输出直流控制电压uc(t)。uc(t)控制压控振荡器的输出频率,以减小输入信号与压控振荡器输出信号之间的相位误差。

理想情况下,压控振荡器输出信号的频率和相位等于输入参考信号的频率和相位,称环路处于锁定状态(同步状态、跟踪状态)。实际情况下,相差不为零,会存在一个很小且恒定的相位误差。

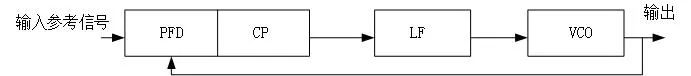

3 电荷泵锁相环

电荷泵锁相环由鉴频鉴相器(Phase FrequencyDetector,PFD)、电荷泵(Charge Pump,CP)、环路低通滤波器(Loop Filter,LF)、压控振荡器(Voltage Controlled Oscillator,VCO)组成。

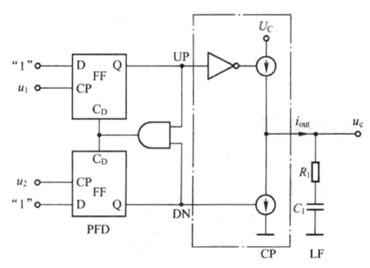

鉴频鉴相器与电荷泵、一阶RC无源环路滤波器的组合原理图如下图。PFD具有UP和DN两个输出端,输出差分信号。UP和DN输出端与电荷泵相连,控制电荷泵的电流开关。UP有效时,UP开关向环路滤波器提供泵电流Ip,当DN有效时,DN开关从环路滤波器吸收泵电流Ip。理想PFD具有第三态,即两个开关都断开,滤波器的输入端浮空。

4 直接数字频率合成器

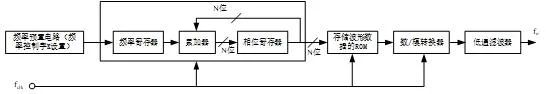

DDS 的基本原理框图如下所示,主要包括频率预置电路、相位累加器、储存波形数据的 ROM、数模转换器及低通滤波器。其中 K 为频率控制字,N 为相位累加数的位数,fclk 为输出时钟频率,fo为输出波形的频率。

相位累加器的 DDS 的核心,由 N 位加法器和N 位相位寄存器组成。在时钟脉冲 fclk 的控制下,加法器将频率寄存器中的频率控制字K 与相位寄存器输出的上一次累加的相位结果相加,以得到本次累加的结果,该结果存入相位寄存器。相位寄存器一方面将该结果反馈到加法器的输入端,在下一时钟脉冲的作用下,加法器继续与频率控制字相加;另一方面又将该累加值作为相位地址对波形 ROM 存储表进行寻址,输出的数据经DA转换器和低通滤波器后得到模拟波形。

编辑:lyn

-

简述锁相环的基本结构2024-08-06 2209

-

锁相环技术解析(下)2023-11-29 2880

-

锁相环是如何实现倍频的?2023-09-02 5833

-

什么是锁相环 锁相环的组成 锁相环选型原则有哪些呢?2023-08-01 7795

-

模拟锁相环和数字锁相环区别2023-02-15 6927

-

MCU锁相环简述(一)2021-11-01 1332

-

锁相环2011-10-26 17708

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6461

-

锁相环电路2009-09-25 7785

-

软件锁相环的设计与应用2008-08-15 1356

-

锁相环原理2007-08-21 5597

全部0条评论

快来发表一下你的评论吧 !