功率MOSFET及其雪崩击穿额定值背后的理论和设计过程中的局限性

电子说

描述

本应用笔记介绍了功率 MOSFET 及其雪崩击穿额定值背后的理论。该文件还讨论了坚固型 MOSFET 的设计和额定值,以及不同的雪崩额定值及其在设计过程中的局限性。

雪崩模式定义

所有半导体器件都具有一定的最大反向电压额定值(功率 MOSFET 的 BV DSS)。高于此阈值的操作将导致反向偏置 pn 结中的高电场。由于碰撞电离,高电场会产生电子-空穴对,这些电子-空穴对会产生倍增效应,从而导致电流增加。流过器件的反向电流会导致高功耗、相关的温升和潜在的器件损坏。

工业应用中发生的雪崩

反激式转换器电路

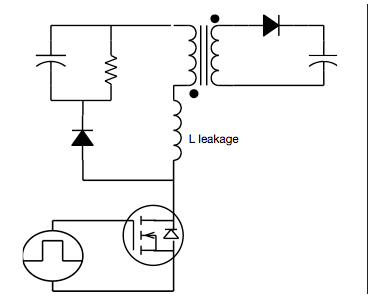

一些设计者不允许雪崩操作;相反,在额定 BV DSS 和 VDD 之间保持电压降额(通常为 90% 或更少)。然而,在这种情况下,可能会出现超出计划的电压尖峰的情况并不少见,因此即使是最好的设计也可能会遇到非频率雪崩事件。图 1 显示了一个这样的示例,即反激式转换器。

反激式转换器电路

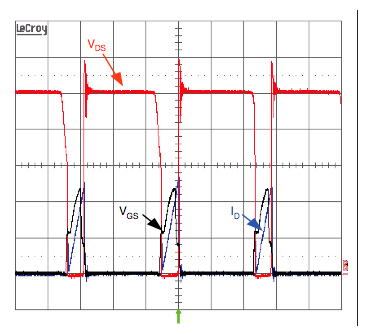

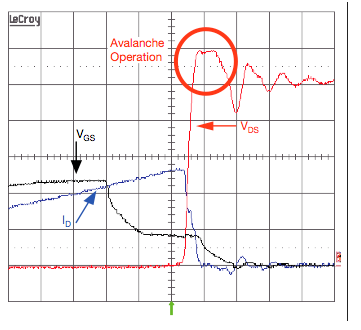

在反激式转换器的 MOSFET 操作期间,能量存储在漏电感中。如果电感未正确钳位,在 MOSFET 关断期间,漏电感通过初级开关放电,并可能导致雪崩操作,如图 2 和 3 中 VDS、ID 和 VGS 与时间的关系波形所示。

雪崩波形下的反激式转换器开关:

雪崩波形下的反激式转换器开关(详细)

雪崩故障模式

一些功率半导体器件设计为在有限时间内承受一定量的雪崩电流,因此可以达到雪崩额定值。其他人会在雪崩开始后很快失败。性能差异源于特定的设备物理、设计和制造。

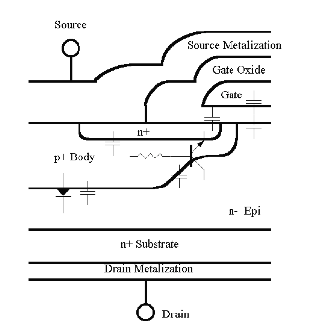

功率 MOSFET 器件物理

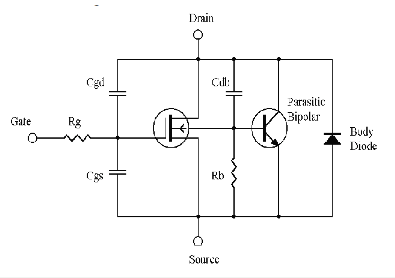

所有半导体器件都包含器件物理设计固有的寄生元件。在功率 MOSFET 中,这些组件包括由于 p 和 n 区之间的结中的电荷转移而产生的电容器、与材料电阻率相关的电阻器、在 p+ 体扩散进入 n- 外延层时形成的体二极管,以及 NPN(双极结型晶体管此后称为 BJT) 序列 (BJT),在 n+ 源极触点扩散的地方形成。请参见图 4 了解包含上面列出的寄生元件的功率 MOSFET 横截面,参见图 5 了解器件的完整电路模型。

功率 MOSFET 横截面:

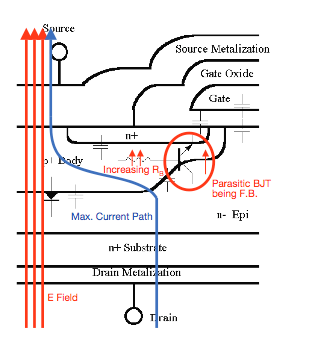

功率MOSFET电路模型在雪崩中,充当二极管的 pn 结不再阻断电压。施加更高的电压会达到临界场,其中碰撞电离趋于无穷大,载流子浓度由于雪崩倍增而增加。由于径向场分量,器件内部的电场在结弯曲处最强。这种强电场会在寄生 BJT 附近产生最大电流,如下图 6 所示。功耗会增加温度,从而增加 RB,因为硅电阻率随温度增加。根据欧姆定律,我们知道在恒定电流下增加电阻会导致电阻两端的电压降增加。当压降足以正向偏置寄生 BJT 时,

雪崩下的功率 MOSFET 截面

功率 MOSFET 用户应注意了解不同供应商之间雪崩额定条件的差异。不是“雪崩稳健”的设备可能会导致意外和看似无法解释的电路故障。一些制造商根本没有对他们的 MOSFET 进行雪崩评级。其他人单独使用统计评级,这不能为更完整的表征和评级提供的稳健操作提供相同的保证。

编辑:ymf

-

MOSFET的失效机理:dV/dt失效和雪崩失效2023-04-15 3266

-

34063的局限性2011-06-12 5325

-

看懂MOSFET数据表,UIS/雪崩额定值(一)2015-11-19 5404

-

功率MOSFET重复雪崩电流及重复雪崩能量2017-09-22 8059

-

FPGA的优势与局限性2017-12-20 7601

-

MOSFET数据表之UIS/雪崩额定值2018-09-05 2691

-

无线网络有什么局限性?2019-08-23 3335

-

看懂MOSFET数据表—UIS/雪崩额定值2022-11-18 798

-

标准硅MOSFET功率晶体管的结构/二次击穿/损耗2023-02-20 3066

-

功率MOSFET雪崩击穿问题分析2009-07-06 6755

-

涡轮流量计使用过程中的局限性2019-07-18 1175

-

功率MOSFET的雪崩特性和额定值详细说明2020-06-08 1481

-

WSN中LEACH协议局限性的分析与改进2021-09-15 933

-

看懂MOSFET数据表,第1部分—UIS/雪崩额定值2022-11-03 816

-

MOSFET的失效机理:什么是雪崩失效2023-02-13 3431

全部0条评论

快来发表一下你的评论吧 !