SMT焊接好坏的检验应该参考哪个标准

描述

Q

芯片sleep电流20uA以上,怀疑是漏电,但做emmi却没发现热点,而且做完emmi之后电流高达220uA,这是为什么?

A

可能分析过程导致样品二次损坏了,这么小的漏电可以通过obirch仔细找找漏 电点,然后再进一步分析和判断失效原因。

Q

为什么BHAST采用差分输入输出的接法,原因是啥?并且都不用外接偏压了?这种接法都不加偏压了,是不是没有电的加速了?为啥这种接法可以起到防止阻抗不匹配的问题?

A

防止差分信号之间因为BHAST 过程中电化学加速腐蚀速度的差异导致impedance mismatch,从而在芯片FT readout的时候出现fail。差分输入输出的接法,仅限于差分信号。你的芯片上应该不至于全部都是差分信号吧,电源管脚和部分GPIO管脚是要加偏压的。

导致阻抗不匹配的原因:差分信号的两端状态一致,腐蚀程度也一致。当然,也可以不用这种推荐接法,和产品的designer 另外研究一种接法,能实现目的即可。

Q

目前发现很多已经上板的芯片测试不良,而且已经量测到不良端口,为什么到厂商那边大部分分析为NTF,有哪几种可能性?比如做过交叉实验,有些IC的时钟信号,我们板端怎么都量测不到12M和24M信号,厂商那边测试12M和24M都没问题,这就很奇怪。

A

建议先让厂商复现问题,这是最关键的。这个需要你们彼此了解测试的条件细节。有时模组厂为了省成本,改变BOM,也会导致质量问题。或者仔细对比芯片每个管脚设置,有时不确定的floating会引起区别。芯片公司内部,系统级测试还分 Scoket Board测试、SLT测试、Reference Board测试,有时候,这3者之间结果有时候也会不同。其实解决这个问题很简单,我们只要能理解,判断pass的标准应该是在使用环境的功能正常,因此,最接近使用环境的测试是Reference Board测试pass才能说是pass。这一点系统厂商和芯片厂商可以达成一致。

可以从下面3个方面,尝试解决测试的差异问题:1、电源, 提高和降低电源,看看是否工作。2、管脚配置,比如Boot Strapping, Config管脚,看看是否和ATE一致,这点可以请厂商帮忙对比。3. 寄存器配置,如果需要配置的话,请厂商对比你们的寄存器和原厂的寄存器配置差异。若是你们的板子和他们自己的板子都复现了,基本就是芯片问题。

Q

有一颗芯片采用LFBGA封装,对ddr与usb差分信号提出了如下要求,结果封装厂反馈说要求过于严格要求放松,否则板厂可能不接单。请问大家我们的要求合理吗?封装厂的说法合理吗?不知道对于DDR封装阻抗一般是怎么要求的?对于差分信号线,是否卡控差分阻抗就可以了,不需要卡控单端阻抗?

A

每个芯片不一样啊,单端、差分数量不一样,在一定层数下,有时候板厂无法同时满足。可以先做一下仿真,当阻抗出现偏差,然后看DDR的工作情况。+/-10%阻抗是比较容易控制的等长比较容易。对于差分信号线,卡控差分阻抗就可以了。

Q

做solder bump时,UBM层设计为:Ti : 1kÅ ,Cu:3kÅ,Cu:8um ,生产为:Ti : 1kÅ ,Cu:3kÅ,Cu:5um,Ni:3um;电性与可靠性方面存在哪些差异?

A

Ni layer 是做为barrier layer,主要目的是防止cu 扩散偏移,但是不加Ni 会导致IMC形成。

IMC的形成与发展,与焊料合金、基底金属类型、焊接的温度与时间以及焊料的流动状态有关。一般而言,在焊料熔点以下温度,IMC的形成以扩散方式进行,速度很慢,其厚度与时间开方成正比;在焊料熔点以上温度,IMC的形成以反应方式进行,温度越高、时间越长,其厚度越厚。普遍认为,很厚的IMC是一种缺陷。因为IMC比较脆,与基材(封装时的电极、零部件或基板)之间的热膨胀系数差别很大,如果IMC长得很厚,就容易产生龟裂。

对于封装基板上的Ni/Au镀层,Ni层表面的镀金厚度应该小于0.08um, 太厚会阻碍IMC形成, Ni层的厚度本身不会影响IMC形成。一般来说IMC层在2--4左右吧,根据不同情况而定。

Q

HAST试验后,有漏电流超标,然后烘烤后,漏电流达到正常值,是否可以判定产品PASS?

A

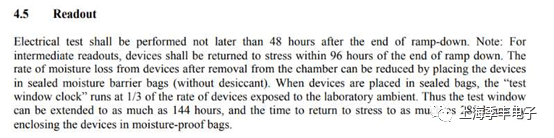

不可以,hast之后有时间要求的,这个时间内必须做ATE。另外,HAST实验考量芯片的封装可靠性,HAST实验后,漏电超标,说明封装是有问题的。烘烤后,再去做ATE,这个实验数据就没有意义。为了避免HAST的结果受环境影响,一般实验后,会做密封处理(不加干燥剂),尽量在48H内做完ATE测试。详细关于读点的注意事项见下图:

Q

QFN封装IC,SMT焊接好坏的检验标准,参考那个标准?

A

IC参考标准:SOLDERABILITY JESD22-B102E。SMT参考标准:IPC一610F。

Q

哪位有JESD671D-2018?

A

可以在JEDEC官网上检索,都是免费下载的。详细网址:https://www.jedec.org/

Q

有没有老化寿命和测试条件之间的关系的资料?

A

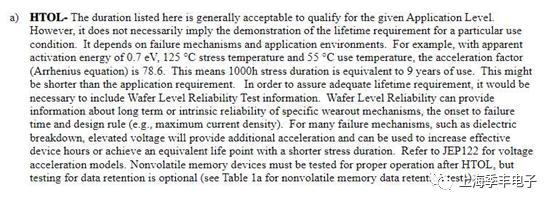

可以参考标准:JESD74, JESD85,JESED47。

Q

光器件接收侧的APD电压只有2.8V正常是45V,量APD对地阻抗是正常的,但是上电后电压就不正常远低于45V,已经排除输入电压的原因。准备继续查光器件内部的APD雪崩二极管,问题是为什么阻抗正常,电压不正常?从哪里入手查呢?

A

先做测良品和不良品的BV-curve,看看漏电从哪起来的。看看曲线是线性还是指数,大概的解决思路就出来了。

Q

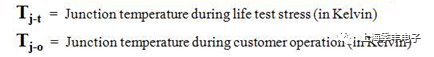

老化试验的早期失效率和等效使用时间计算中的Stress Temperature是对应芯片结温吗?Normal Operating Temperature对应规格书上的Operating Temperature上限吗?

A

个人理解其实应该是结温,不过对于大部分不发热的芯片或者加电功率很小的产品,环境温度近似等于结温。应该是自生温加上环境温度。对于Si 产品没有太大差异,但是对于功率器件,可就完全不一样了哦。

温度的定义可以参考标准:JEDEC74 ,或者参考下图。

Q

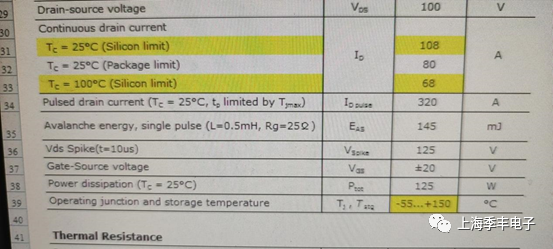

对于功率器件,HTOL试验的环境温度只要满足结温的要求就可以了吗?

A

结温一般由热阻或者红外测试出来,然后加上环境温度也就是温箱的环境温度,就差不多是标准里要求的150℃了。

个人理解:规格书工作温度应该就是可靠性考核的温度。要限定不同环境温度下的工作电流极限,防止结温超过这个温度。下图规格书中HTGB HTRB的可靠性温度也是150℃。

Q

u/b hast,precon等可靠度报告中为什么不能放如器件sn#, date code, 前后比对的数据呢?有哪个规范中有明确么?

A

一般的报告是不放的,如果客户有强烈的需求,那就跟人家说清楚,客户需求是重点。如果客户非要要求,不得不放。若是ort 批次抽检,需要写明lot id。

编辑:jq

-

smt电子元器件焊接可靠性判断标准有哪些2023-08-22 5371

-

SMT贴片加工的手工焊接是怎么进行的?2023-07-17 2251

-

SMT锡膏印刷外观检验判定标准2022-11-07 1644

-

SMT贴片检验有哪些标准2020-07-19 9762

-

smt贴片在加工前的检验方法都有哪些2020-06-16 2028

-

SMT贴片加工中的质量检验标准分析2020-03-17 3270

-

决定SMT贴片质量好坏的三大关键工序介绍2019-11-15 6957

-

smt贴片检验的标准是什么2019-08-30 15907

-

smt贴片检验标准2019-04-16 12356

-

SMT加工费是检验电子加工厂的一个标准吗?2018-01-04 3739

-

SMT焊接检验标准及元器件推力标准2017-03-15 6381

-

耀谷公司SMT元件焊接及检验技巧专题交流会2010-10-29 4162

-

SMT通用检验标准2009-10-06 1916

全部0条评论

快来发表一下你的评论吧 !