基于FPGA的自适应阈值分割算法实现

今日头条

描述

在图像预处理中经常会碰到图像分割问题,把感兴趣的目标从背景图像中提取出来,而经常使用的是简单的全局阈值分割配置,用一个固定常数作为二值分割阈值,从而得到一个二值图像,如果更复杂些,可以使用大律法实现自适应全局阈值分割。但是在有些场景下,比如光线不均匀照射下,全幅图像中不同位置的像素点,光强有强有弱;因此,如果再使用全局阈值来处理就失效了,如下图所示是图像的大律法OTSU分割效果。由此可以看出,因为图像边缘光强较中间位置弱,导致图像分割有缺陷,使得分割后二值图像边缘为1,而中间较亮的地方分割成功。

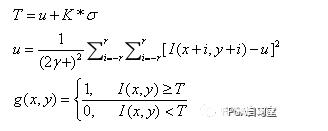

如何解决光线不均匀带来的影响?一种典型的处理方法就是采用局部自适应阈值分割。根据像素邻域块的像素值分布来确定该像素位置上的二值化阈值。这样做的好处在于每个像素位置处的二值化阈值不是固定不变的,而是由其周围邻域像素的分布来决定的。亮度较高的图像区域二值化阈值通常较高,而亮度较低的图像区域二值化阈值则会相应地变小。不同亮度、对比度、纹理的局部图像区域将会拥有相对应的局部二值化阈值。

FPGA实现:

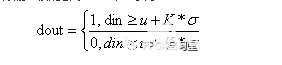

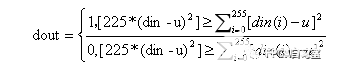

因此,我们可以把FPGA实现分成2个部分实现,一个是左边的不等式计算,一个是右边不等式计算。两者都要使用当前窗口内的计算的像素均值u,如下FPGA实现原理图:

左边不等式:由于均值计算需要一定延时;因此,需要把当前像素数据raw_data Delay后再与Mean_cal 计算的均值u 相减,然后平方(Square)最后乘以窗口像素个数225(15x15),从而完成左边不等式的计算。

最后,两边不等式比较得到阈值分割结果。

如下如所示,是matlab和modelsim 联合仿真的结果,左边是灰度原图,右边是基于Verilog算法之后 matlab 复现图,可以看出分割的效果还不错.

-

改进自适应GACV的水下图像分割算法研究2021-09-22 1083

-

基于FPGA的自适应LMS算法的实现2021-05-28 1313

-

使用双阈值自适应分割的轴承滚子表面缺陷提取技术研究说明2019-10-14 1252

-

怎么设计基于FPGA的高速自适应滤波器?2019-08-23 2777

-

如何使用阈值自适应忆阻器Hopfield神经网络进行关联规则挖掘算法2019-05-08 1444

-

基于自适应阀值分割的慢速小目标检测算法2017-11-09 900

-

LMS自适应算法的FPGA设计与实现_陈亮2017-03-19 1184

-

新阈值函数的自适应去噪2017-01-03 766

-

【Banana Pi M1+申请】阈值自适应视频边缘检测算法的嵌入式快速实现2016-06-20 3147

-

基于FPGA的高速实时图像采集和自适应阈值算法2012-08-11 4222

-

基于FPGA的高速实时图像采集和自适应2011-09-14 1091

-

基于多层采样多阈值的目标分割算法2009-12-18 1968

-

一种带验证的自适应镜头分割算法2009-12-16 847

-

一种自适应多尺度积阈值的图像去噪算法2009-11-11 632

全部0条评论

快来发表一下你的评论吧 !