log2在verilog中到底有什么用

描述

很多小伙伴对上一篇文章讲的取对数没感觉,觉得这个没什么用。确实很多时候用不着,verilog本身不够灵活,所以很多时候我们也就没想把她写的多简介灵活,而且受限于编译器的支持,很多灵活的语法不能被编译成电路,所以有这种想法情理之中,毕竟花大把时间去玩一个函数发现他局限性很大那确实收益太少。

那么他到底有什么用?

如果大家要设计一个深度1024的fifo,那么地址位宽取多大合适?*╭︎( ˙º˙)╯︎*

当然是10位,log2(1024)

所以可以如下定义

parameter deepth = 1024;

parameter width = $clog2(deepth);

这样就把两个参数关联起来,调整代码的时候提高了可维护性也更方便。

但是到此为止了吗?

不知道大家有没有对做完fft以后取对数很苦恼,比如fft输出实部虚部各16bit,平方和开根号以后暂且也以16bit表示,那么怎么取对数呢?第一种方法是查表,第二种是传到上位机,让他处理。很多时候FPGA上确实不需要取对数这个操作,但是如果受限于高速接口,比如万兆网,pcie等接口速率希望压缩数据的时候对fft结果取对数无疑是一个很有必要的操作。毕竟log10这个对数可以把16位的数压缩到8位以内。所以查表确实可行,但是位数是24位呢,那情况就多了太多了,32位呢?

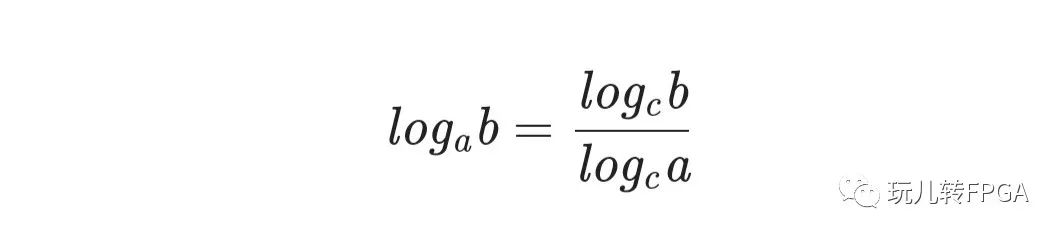

所以取对数这时候就有价值了,但是这是10为底的对数,和2为底的对数有什么关系?当然有关系,换底公式啊!

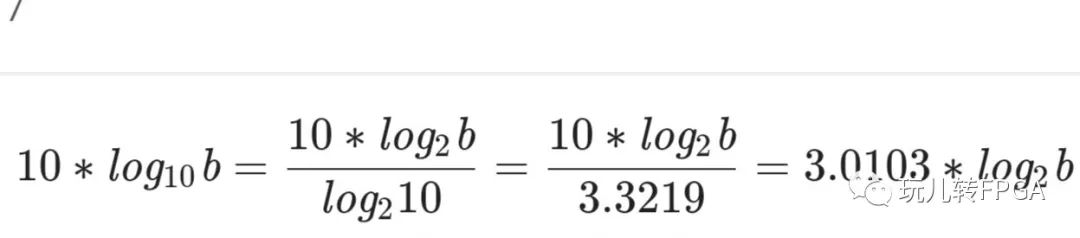

多数时候fft之后我们计算10*log10或者20*log10,那么就等价于如下操作

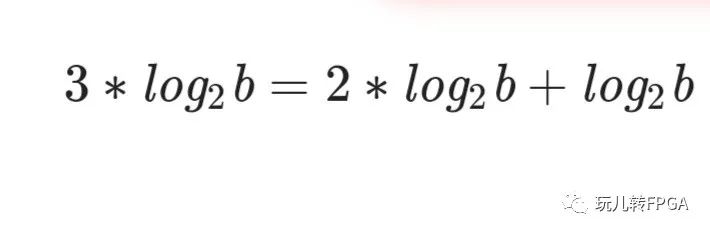

忽略3后面的小数影响的话,那么可以近似为

多震撼的结论,所以数学好真的很有必要啊!当然你想更高精度,可以对换底公式以后的分子分母同时放大10的幂次方倍,然后再往下计算,这里留给读者自行思考。

是不是很累,很复杂?

那么我告诉你,verilog2005有log10的系统函数,哈哈哈哈哈,意不意外???

责任编辑:haq

-

24位或者说高分辨率的AD到底有什么用呢?2025-01-07 480

-

请问GUI_DEBUG_LOG是干什么的?2019-05-30 1107

-

反码位是什么?到底有什么用?2021-05-07 2209

-

64-Kbit FRAM是什么?64-Kbit FRAM到底有什么用途?2021-06-17 1691

-

笔记本固态硬盘到底有什么用呢2021-09-08 1957

-

TVS管在工作过程中与电压和电流到底有何奥秘2021-10-09 1828

-

模拟看门狗到底有什么用处呢2022-01-17 1494

-

异常处理向量表的设置中DCD这些伪指令到底有什么用?2023-02-28 1441

-

board中的Kconfig到底有什么用?2023-08-02 2200

-

数据可视化到底有什么用?2018-02-05 26891

-

工业互联网, 你到底有啥用?2020-03-01 4366

-

NFC是什么NFC到底有什么用处2020-02-04 152066

-

PCB设计中开窗有什么用?如何设计?2021-05-01 30807

-

npu是什么意思?npu芯片是什么意思?npu到底有什么用?2023-08-27 47577

-

IPv6到底有什么用,给我们生活带来哪些变化?2024-03-29 2825

全部0条评论

快来发表一下你的评论吧 !