两个网络相关的开源项目详解

描述

今天介绍两个(only two)网络相关的开源项目。

Alex的verilog-ethernet之前在介绍PCIe项目时有介绍过Alex的项目,当时重点介绍了PCIe。今天主要介绍他的ethernet项目。

❞介绍用于1G、10G 和 25G 数据包处理(8 位和 64 位数据路径)的以太网相关组件的集合。包括用于处理以太网帧以及 IP、UDP 和 ARP 的模块以及用于构建完整 UDP/IP 堆栈的组件。包括用于1G和 10G/25G 的 MAC 模块、一个 10G/25G PCS/PMA PHY 模块和一个 10G/25G 组合 MAC/PCS/PMA 模块。包括用于实现需要精确时间同步的系统的各种 PTP 相关组件。还包括使用cocotbext-eth 的完整 cocotb 测试平台代码。

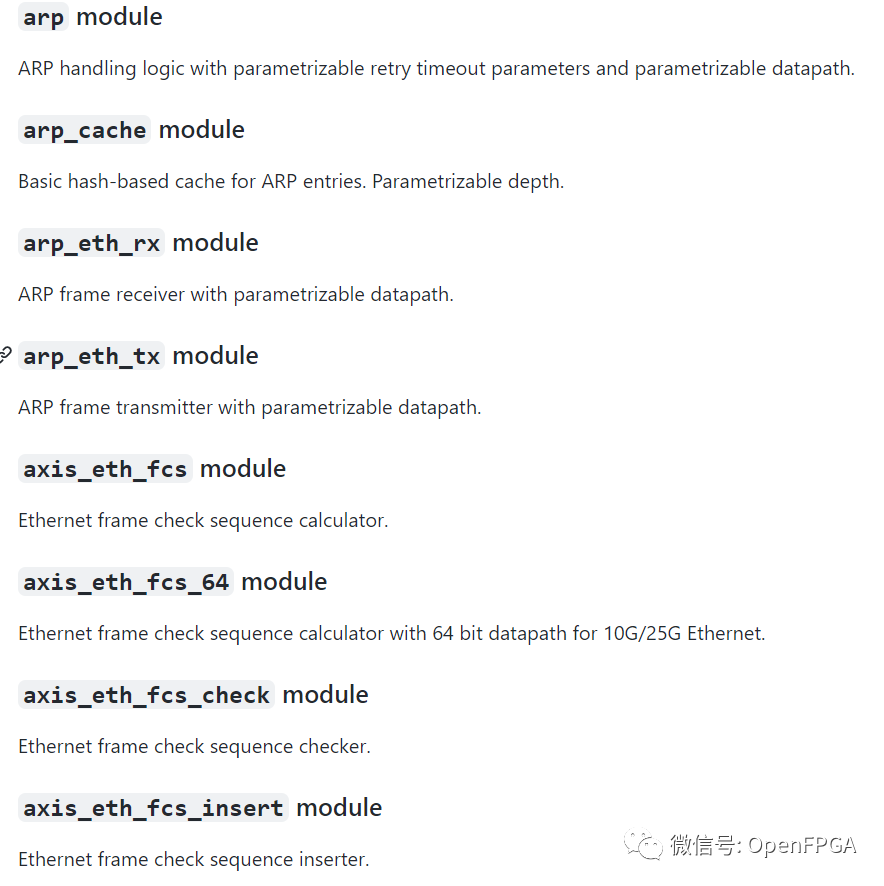

组件说明:仅对于 IP 和 ARP 支持,请使用ip_complete(1G) 或ip_complete_64 (10G/25G)。

对于 UDP、IP 和 ARP 支持,请使用udp_complete(1G) 或udp_complete_64 (10G/25G)。

1G和 10G/25G MAC 模块顶层文件eth_mac_*,具有各种接口和带/不带 FIFO。10G/25G PCS/PMA PHY 模块顶层文件是 eth_phy_10g. 10G/25G MAC/PCS/PMA组合模块顶层文件是 eth_mac_phy_10g.

PTP 组件包括可配置的 PTP 时钟 ( ptp_clock)、ptp_clock_cdc用于跨时钟域传输 PTP 时间的 PTP 时钟 CDC 模块 。以及用于从 PTP 时间精确生成任意频率的可配置 PTP 周期输出模块。

其中cocotbext-xxx是仿真测试模型(cocotb is a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.cocotb是一套基于python的用于构建仿真及测试用例的lib库)。

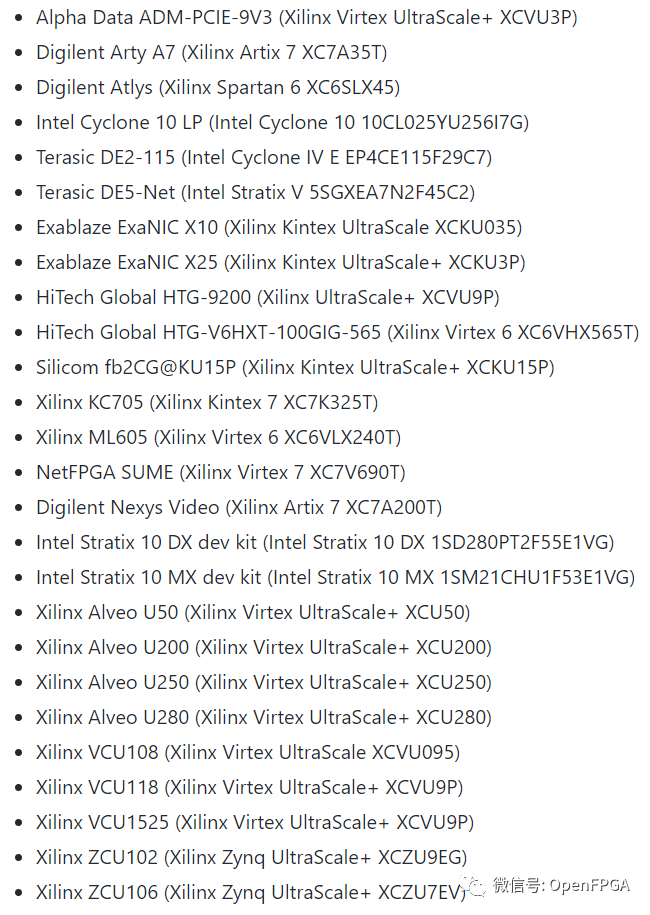

已经验证的板卡

基本市场上官方的板卡都有测试,从Xilinx S6到ZCU106,Intel Cyclone10到Stratix10 大小芯片都支持。

优秀的 Verilog/FPGA开源项目介绍(三)- 大厂的项目

其他说明README中也有模块的说明:

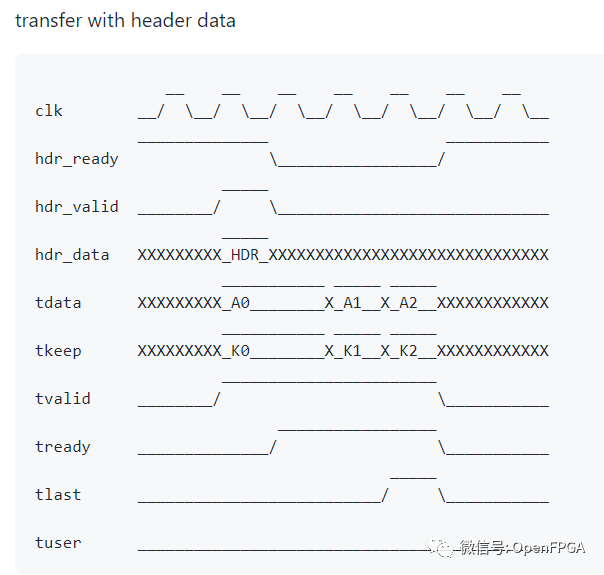

以及相关接口的时序说明:

优秀的 Verilog/FPGA开源项目介绍(二)-RISC-V

测试平台的使用也有详细的说明。

业界第一个真正意义上开源100 Gbps NIC Corundum对于需求100G网卡的朋友,一定要看看这个开源项目,先放开源地址:

❝

https://github.com/ucsdsysnet/corundum

❞介绍Corundum 是一种基于 FPGA 的开源高性能 NIC。功能包括高性能数据路径、10G/25G/100G 以太网、PCI express gen 3、定制的高性能、紧密集成的 PCIe DMA 引擎、1000+ 传输、接收、完成和事件队列、分散/收集DMA、MSI 中断、多个接口、每个接口多个端口、每个端口的传输调度,包括高精度 TDMA、流散列、RSS、校验和卸载和本地 IEEE 1588 PTP 时间戳。包含一个与 Linux 网络堆栈集成的 Linux 驱动程序。广泛的仿真框架促进了开发和调试,该框架涵盖了从一侧的驱动程序和 PCI express 接口的仿真模型到另一侧的以太网接口的整个系统。

Corundum 有几个独特的特征。首先,传输、接收、完成和事件队列状态高效地存储在块 RAM 或ultra RAM中,从而支持数以千计的可单独控制的队列。这些队列与接口相关联,每个接口可以有多个端口,每个端口都有自己独立的调度程序。这实现了对数据包传输的极其细粒度的控制。结合 PTP 时间同步,这可以实现高精度 TDMA。

Corundum 还提供了一个用于实现自定义逻辑的应用程序部分。应用部分有一个用于控制的专用 PCIe BAR 和许多提供对核心数据路径和 DMA 基础设施的访问的接口。

支持的板卡Alpha Data ADM-PCIE-9V3 (Xilinx Virtex UltraScale+ XCVU3P)

Exablaze ExaNIC X10/Cisco Nexus K35-S (Xilinx Kintex UltraScale XCKU035)

Exablaze ExaNIC X25/Cisco Nexus K3P-S (Xilinx Kintex UltraScale+ XCKU3P)

Silicom fb2CG@KU15P (Xilinx Kintex UltraScale+ XCKU15P)

NetFPGA SUME (Xilinx Virtex 7 XC7V690T)

Xilinx Alveo U50 (Xilinx Virtex UltraScale+ XCU50)

Xilinx Alveo U200 (Xilinx Virtex UltraScale+ XCU200)

Xilinx Alveo U250 (Xilinx Virtex UltraScale+ XCU250)

Xilinx Alveo U280 (Xilinx Virtex UltraScale+ XCU280)

Xilinx VCU108 (Xilinx Virtex UltraScale XCVU095)

Xilinx VCU118 (Xilinx Virtex UltraScale+ XCVU9P)

Xilinx VCU1525 (Xilinx Virtex UltraScale+ XCVU9P)

Xilinx ZCU106 (Xilinx Zynq UltraScale+ XCZU7EV)

说明这个项目很多都引用了上面《Alex的项目》,可以算是上一个项目的扩展。测试等文档也很完全。框图如下

责任编辑:haq

-

如何设置两个路由器使用同一个Wi-Fi网络?2023-12-11 16671

-

开放原子开源基金会与Eclipse基金会正式签署协议,创造了两个第一2023-11-21 1136

-

关于两个Python开源识别工具的效果2023-10-17 1525

-

这两个PCB相关项目开工2023-09-20 1276

-

两个防反接电路原理详解2023-07-10 3746

-

两个网络IP地址是否在同一个段中的判断方法2023-06-02 15244

-

两个LED和两个按钮的使用2023-01-30 611

-

两个电机的电路开源2022-08-03 535

-

推荐两个工作流的springboot项目2022-03-18 2452

-

两个运动员赛跑计时的秒表项目的verilog设计资料免费下载2020-08-04 1324

-

如何在两个局域网内共享一台打印机 ,常用网络命令及命令实例详解2020-06-09 2151

-

重庆两个集成电路类项目开工2019-01-18 4729

-

使用Jflash软件合并两个bin文件2017-11-22 1118

-

CAN-bus网络中,出现具有相同ID段的两个节点会发生什么?2017-09-14 11340

全部0条评论

快来发表一下你的评论吧 !