芯粒技术对延缓摩尔定律至关重要

工艺/制造

描述

-台积电 OIP 生态系统论坛揭示的挑战和解决方案

上海2021年10月27日 /美通社/ -- 世芯电子设计研发副总裁 James Huang 表示,世芯电子将芯粒革命视为摩尔定律极具成本效益的延伸。

世芯灵活的商业模式是芯粒和先进封装的实现的关键。这种灵活性最大限度地提高了内部工程专业知识和ASIC设计的兼容性。在台积电 2021 年开放创新平台的技术演讲中,James Huang 强调,芯粒和先进封装提供了与单片 SoC 相比具有竞争力的成本结构,同时保持了相近的性能和功耗。

James Huang 引用了两项对芯粒/封装发展至关重要的技术:一种是台积电的 3DFabric 和 CoWos® 组合技术。 另一个是世芯的 APLink 芯粒间互联 I/0。

APLink 芯粒间互联 I/0 支持多个芯粒之间的高速数据交换。APLink 1.0 的目标是台积电的 12 纳米工艺,而 APLink 2.0 的目标为7纳米工艺。5纳米工艺的APLink 3.0目前正在进行测试芯片结果评估,已达到目标线速。APLink1.0和2.0的线路速率分别为1Gbps和4Gbps。

超越眼前的视野,James Huang 向与会者展示了未来的高峰。在详细介绍 APLink 4.0 时,他透露了以 3 纳米为目标的芯粒间互联 IP。

APLink 4.0 的互连将采用以标准内核电压运行的源同步 I/O 总线。每个 PHY 模块以 12Tbps 的速度运行,每条 DQ 线路的速度高达 16Gbps,但只有 5 纳秒的延迟。这些规格能支持可靠的系统操作。

APlink 4.0 IP 将支持北/南和东/西方向以及对称的 PHY 布局排列,这最大限度地减少芯粒间互联的信号线长度。

“真正将未来变为现实的是一种灵活的商业模式,它更符合未来技术创新需求。”James Huang 指出。

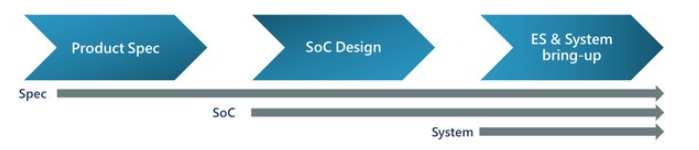

在实现多芯粒系统设计时,世芯与客户的合作模式提供多个起始点,包含产品规格制订、SoC 设计或系统调试与量产等合作起始点。

-

什么是摩尔定律?2023-08-05 8079

-

晶圆和摩尔定律有什么关系?2011-12-01 6017

-

介绍28 nm创新技术,超越摩尔定律2012-08-13 2682

-

摩尔定律也适用于EPON芯片商用之路?2011-09-27 2571

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 4308

-

摩尔定律推动了整个半导体行业的变革2019-07-01 4485

-

摩尔定律还能走多远看了就知道2021-02-01 2094

-

摩尔定律在测试领域有哪些应用?2021-04-13 2311

-

请问摩尔定律死不死?2021-06-17 1982

-

IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?2021-07-22 1693

-

摩尔定律,摩尔定律是什么意思2010-02-26 1994

-

摩尔定律_摩尔定律是什么2012-05-21 2871

-

摩尔定律是什么_摩尔定律提出者及含义2018-03-09 33275

-

后摩尔时代保鲜剂芯粒的优点有哪些2020-01-20 2200

-

摩尔定律的演变 后摩尔时代的芯粒技术2020-11-05 4197

全部0条评论

快来发表一下你的评论吧 !