主流半桥驱动芯片如何发展:先增效再降本

电子说

描述

电子发烧友网报道(文/李宁远)在直流电机中,单片机提供的电压电流一般不足以驱动直流电机,只能作为驱动信号。所以要在它们之间加一个Motor Driver,即驱动器。半桥驱动器的作用就是通过功率管产生交流电触发信号,从而产生大电流进一步驱动电机。相比于全桥,半桥驱动电路成本偏底,电路也更容易形成,而全桥电路成本高,电路相对复杂。当然,全桥电路不容易产生泻流,而半桥电路在振荡转换之间容易使波形变坏,产生干扰。

在半桥驱动电路中一般都会加入死区设置,如果不加入死区,那么在一个电力电子器件尚未完全关闭时另一个电子器件就已经完全开启,这样会形成短路,从而烧坏器件。因此半桥驱动芯片中如何降低死区时间要求,是一处十分体现性能的要点。

其实主流大厂的这一类型芯片,性能都非常高,各家独有技术加持下的产品可以说各有所长,在效率拉不开明显差距的情况下,降低成本提升性价比成了主流半桥驱动芯片另一个比拼的重点。

Infineon 半桥驱动芯片

Infineon在半桥驱动上可以说是集大成者,他们的半桥驱动芯片通常带有两个互锁通道。这里不再对IR2104这款耳熟能详的半桥驱动做赘述,大家对他太熟悉了。

我们来看看最新推出的650 V半桥驱动,一个绝缘体上硅(SOI)栅极驱动器IC,具有高电流(2.5 A)和低电流(0.7 A)两个选项,强度和抗扰度都很优秀。

首先说说英飞凌的绝活,绝缘体上硅(SOI)技术。该技术本质上是一种高压的电平转换技术,集成了BSD,每个晶体管都被埋入的二氧化硅隔开。该技术表现在芯片强大的抗负瞬态电压能力以及低电平转换损耗上。

2ED2101S06F就是基于该技术的半桥栅极驱动器。该系列在高边和低边栅极驱动上有0.29 A拉电流和0.7 A灌电流。SOI给该器件带来的抗负瞬态电压能力足有100V,在行业内绝对的领先。同时,由于器件中不存在寄生晶闸管结构,因此在所有温度和电压条件下都不会发生闭锁。

该器件在延迟会上稍逊一些,为90ns,但这不影响出色负瞬态电压带来的极高耐用性和抗噪性,以及SOI技术带来降低50%电平转换损失这些极优异的性能。除此之外,集成BSD在节省空间,降低BOM成本上很有优势。

ST 半桥驱动芯片

ST电机驱动器涵盖也非常广,从单桥到半桥到多通道驱动器。在高压应用上,ST的半桥驱动优势会比起同行更明显,其中一个主要原因就是独家的BCD“offline” 技术。

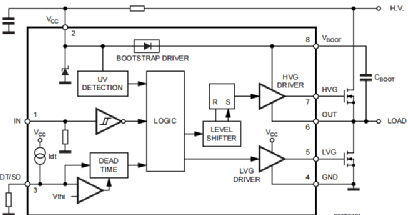

(L6384E,ST)

上图中的L6384E是ST旗下高压半桥驱动器,即采用了BCD“offline” 技术。通过该技术,L6384E高侧浮动部分能够在高达600 V的电压轨下工作,两个设备输出可以分别接收650 mA和400 mA,但由于是单输入配置,只有一个输出会驱动高压。死区时间功能可进一步防止两股输出的交叉传导,还能通过连接到DT/SD引脚的外部电阻器进行调节。

在性能指标上,除了650 mA和400 mA的驱动能力,L6384E能提供全温度范围内±50 V/ns的dV/dt抗扰度。在1nF负载下,开关在rise阶段延迟仅为50ns,在fall阶段延迟也只有30ns。同时,UVLO 保护和 V CC电压钳技术也给予了该器件充足的可靠性。

L6384E保证了保证低压侧和高压侧部分之间的匹配延迟,从而简化设备的高频操作。逻辑输入与CMOS兼容,便于与控制设备接口。

同样的,该器件内部也集成了BSD,效率提高还不够,还要让设计更紧凑。

TI 半桥驱动芯片

这里没有选取TI的高压系列,我们来看看TI的低压半桥栅极驱动器,TI低压系列性能足够稳定,系统也足够可靠。在低压应用上TI没有集成BSD,毕竟不是高压应用,但在效率提高上TI通过降低死区时间让效率更近了一步。

一般将半桥驱动按总线电压分为低压高压两类,低于120V的半桥驱动器相对有更快的传播延迟,可实现更快的切换并提高整体系统效率。

UCC27282,120V半桥栅极驱动器,是TI在低于120V半桥驱动应用下最重要的产品之一。UCC27282属N沟道MOSFET驱动器,通过此器件可在基于半桥或同步降压配置的拓扑中控制两个N沟道MOSFET。该系列有一项极为突出的能力,因为UCC27282具有3.5A的峰值灌电流和2.5A的峰值拉电流以及较低的上拉和下拉电阻,因此在MOSFET米勒平台转换期间,器件能以最小的开关损耗驱动大功率MOSFET。

为了保证器件稳定性和灵活性,UCC27282配置了很多功能。输入引脚和HS引脚能够承受较大的负电压,输入引脚为-5V,HS引脚为-14V,因此提高了系统稳定性。输入互锁进一步提高了高噪声应用中的稳健性和系统可靠性。在高频应用中5V UVLO容许极端的工况,还能提升效率。

在死区设置上,UCC27282较小的16ns传播延迟和1ns匹配延迟可最大限度降低死区时间要求,这是TI在提升效率上的技术关键。

小结

在半桥驱动上,这三家几乎在行业内有压倒性的优势,这几大厂商都有自己的独有技术来降低电平转换损耗和死区时间以此来提高效率,同时集成BSD来减少成本节省空间也渐成行业趋势,尤其是在高压应用领域,毕竟性价比是用户极为看重的。

声明:本文由电子发烧友原创,转载请注明以上来源。如需入群交流,请添加微信elecfans999,投稿爆料采访需求,请发邮箱huangjingjing@elecfans.com。

编辑:jq

-

无线充电器方案XS016MCU+全桥/半桥驱动芯片2018-12-07 8323

-

半桥驱动电路元件损坏的情况2018-12-18 5113

-

半桥驱动电源电路2011-06-19 16320

-

MOSFET半桥驱动芯片IR21112011-07-19 13510

-

半桥驱动电路工作原理及作用2016-08-05 113971

-

主流半桥驱动芯片如何发展:先增效再降本2021-10-28 10356

-

荣湃半桥驱动芯片具备哪些出色性能表现2022-10-11 10224

-

EG2133三相独立半桥驱动芯片中文手册2022-11-21 4531

-

半桥驱动芯片IR2104S典型电路设计方案2023-01-09 25839

-

ID2005半桥igbt驱动芯片-国产200V半桥驱动芯片2022-04-20 2527

-

半桥驱动器芯片的组成、特点、原理及操作规程2024-01-15 3704

-

半桥驱动电路的作用及设计要点2024-02-05 9579

-

矽力杰车规级多通道半桥驱动2024-02-19 4078

-

LM2104:高效半桥驱动芯片的技术剖析与应用指南2026-01-07 499

-

SGM42553:3A 三相半桥电机驱动芯片应用分析2026-03-27 736

全部0条评论

快来发表一下你的评论吧 !