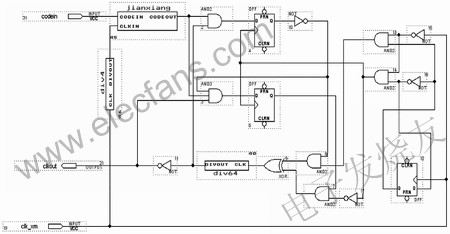

基于FPGA的锁相环位同步提取电路

保护电路图

133人已加入

描述

该电路如图所示,它由双相高频时钟源、过零检测电路、鉴相器、控制器和分频器组成。

欢迎转载,本文来自电子发烧友网(http://www.elecfans.com/)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于锁相环法的载波提取方案2025-01-07 295

-

数字锁相环提取位同步信号的原理2024-10-01 2471

-

求一种基于FPGA的提取位同步时钟DPLL设计2021-05-06 1225

-

求一种锁相环位同步提取电路的设计方案2021-04-29 1359

-

基于FPGA实现电路的同步提取性能设计2019-04-19 4228

-

详解FPGA数字锁相环平台2017-10-16 2154

-

用FPGA实现数字锁相环2016-06-07 1283

-

锁相环2011-10-26 17599

-

锁相环电路2009-09-25 7687

-

锁相环电路的设计2009-07-25 2278

-

基于FPGA的全数字锁相环设计2009-06-26 862

-

模拟锁相环与载波同步实验2009-04-01 9532

-

锁相环原理2007-08-21 5469

全部0条评论

快来发表一下你的评论吧 !