系统级封装SiP多样化应用以及先进封装发展趋势

描述

因新冠疫情影响,第十九届中国半导体封装测试技术与市场年会(CSPT 2021)延后举行并以在线直播的方式召开,日月光研发中心副总经理洪志斌博士透过预录影片解析系统级封装SiP多样化应用以及先进封装发展趋势。

系统级封装SiP、扇出型封装Fan Out以及2.5D/3D IC封装等先进封装不仅可以最大化封装结构I/O及芯片I/O,同时使芯片尺寸最小化,实现终端产品降低功耗并达到轻薄短小的目标。

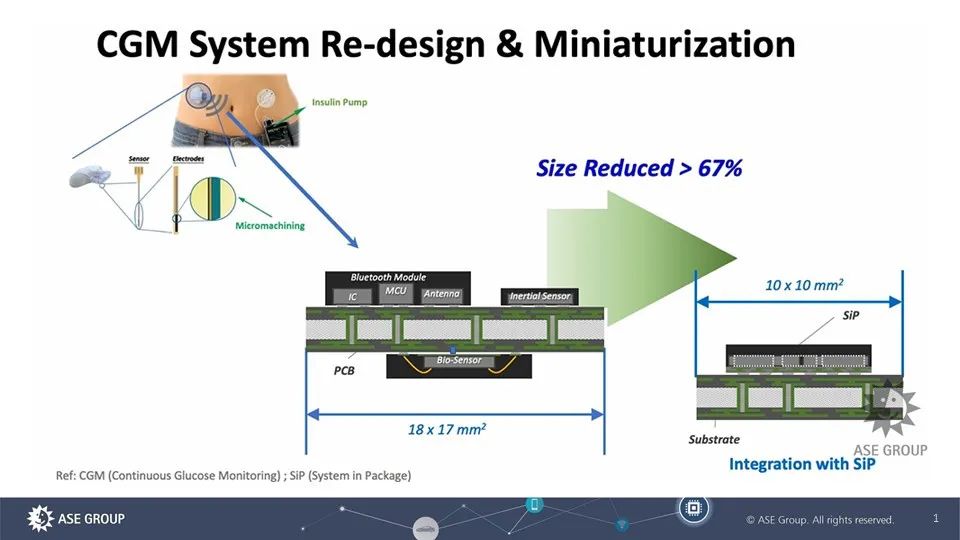

本次演讲洪博士特别举例说明系统级封装SiP应用在健康医疗上的高性能解决方案。以血糖监测系统CGM为例,洪博士指出,系统级封装SiP解决方案将不同的MCU、ASIC、天线,以及各种不同功能的传感器集成一个更小的系统级封装SiP结构中,使系统的总尺寸减小60%但性能大为提高。

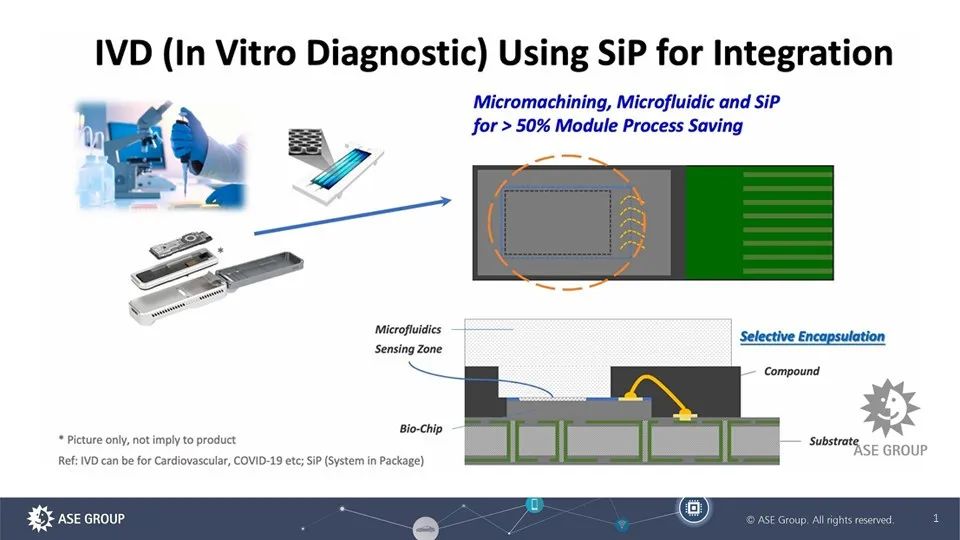

另一个案例是体外诊断模块IVD,透过系统级封装SiP技术,将基于PCB的模块转移到基板结构更小的SiP模块,结合Wire Bond和选择性塑封技术,在基板结构的顶端可整合传感芯片。利用基板结构,许多不同的应用例如针对微流体用途的需求可在其顶部加上玻璃支架,成为尺寸更小的多用途微流体测量模块。

根据不同的应用需求,可选择最适合的封装技术,而不同的封装技术都有其独特的定位与特性,其中最典型的技术包括系统级封装SiP、扇出型封装Fan Out、2.5D/3D IC封装以及小芯片Chiplet技术。

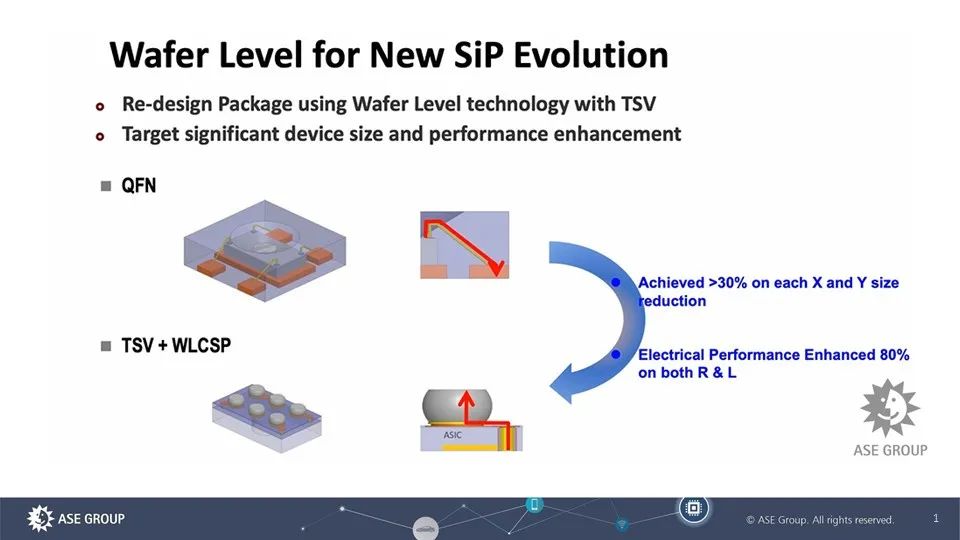

系统级封装SiP是晶圆级封装技术的进一步发展,将QFN转成尺寸更小、有TSV硅穿孔的芯片级尺寸封装CSP,该技术不仅减少30%的XY面积尺寸,同时减少80%的电阻,从而增强封装结构的电气效能。

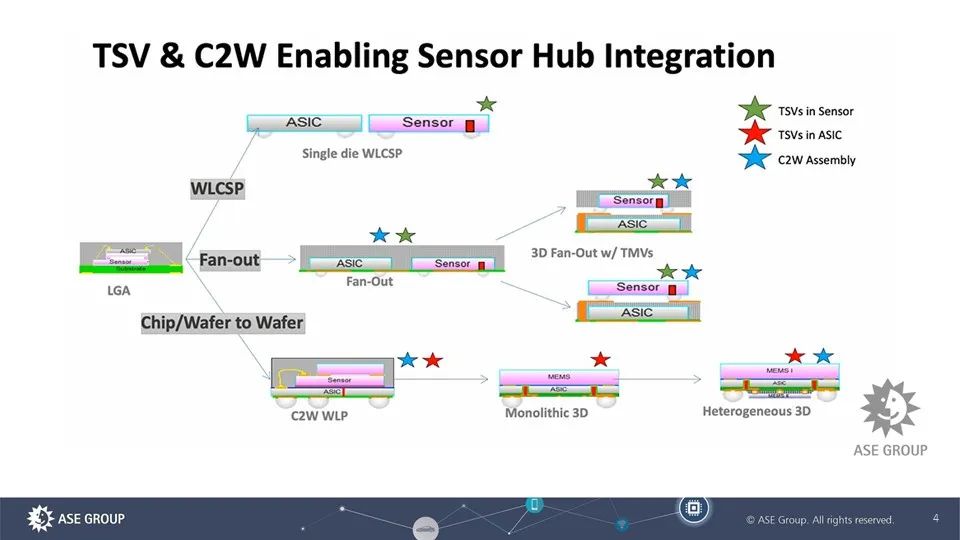

洪博士以传感器整合器举例说明晶圆级封装技术的特性。下图为例,从Leadframe或基板技术开始,如果运用晶圆级封装在不同元件的顶部装有ASIC或传感器,在中间部分可以看到不同的组合,如包含ASIC和传感器的组件,既可以并排放置,也可以把有TSV结构的芯片放在另一个没有TSV结构的芯片上面。在这个封装件的底部也可以采用多种不同的封装方式,例如可使用塑封技术封装或选择不同TSV结构的元件进行封装,也可以采用Flip Chip的封装堆叠,或利用Wire Bond打线技术进行集成。

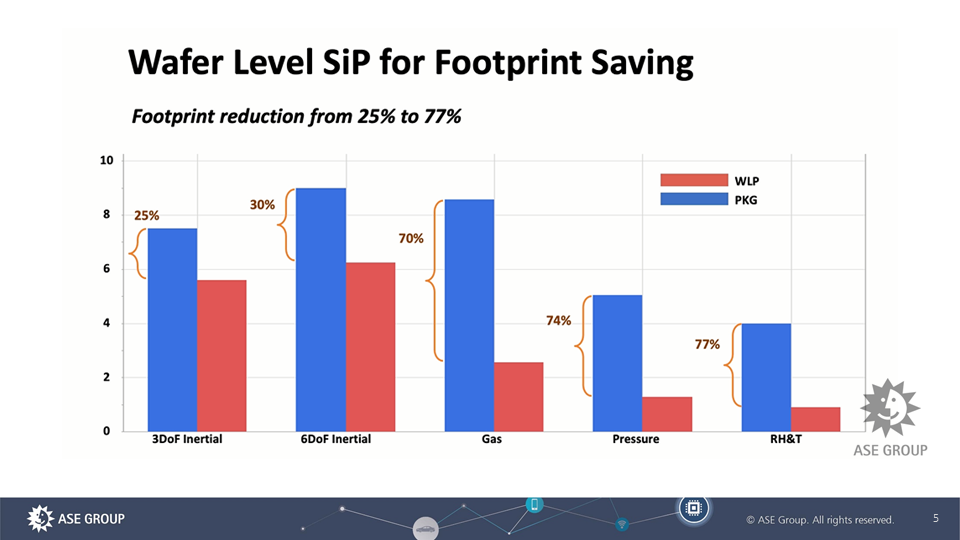

晶圆级系统级(Wafer level SiP)封装在不同的应用中可获得不同的附加效益。举例3D的惯性传感器,还有气体传感器、压力传感器、湿度传感器和温度传感器,从以下图表中可以看到尺寸大大缩小,分別缩小25%, 有些可以达到缩小77%。

· 先进封装趋势 ·除此之外, 不同于系统级封装SiP,扇出型封装Fan Out具有灵活的RDL设计、更细的RDL线宽和空间、大约减少3层基底层等特性,不仅可调整系统性能,更可实现约高5倍的性能控制。因此更高频率的应用、更好的性能和成本效益的扇出型封装Fan Out适用于智能手机、边缘计算和物联网(IoT)等领域。

先进封装另一种典型技术是2.5D/3D IC封装,它具有集成GPU、CPU和内存以及去耦电容的优势,具有超高布线密度、超高I/O密度和I/O间距可扩展性等特性,以TSV(通过硅通孔)的硅插入器作为平台,弥合组装基板和IC板之间的细间距能力差距,同时有助于保持焊盘间距缩放路径而不受组装基板技术的限制,可用于高端GPU、移动AP、大数据中心与5G基础设施的路由器、人工智能加速器等领域。

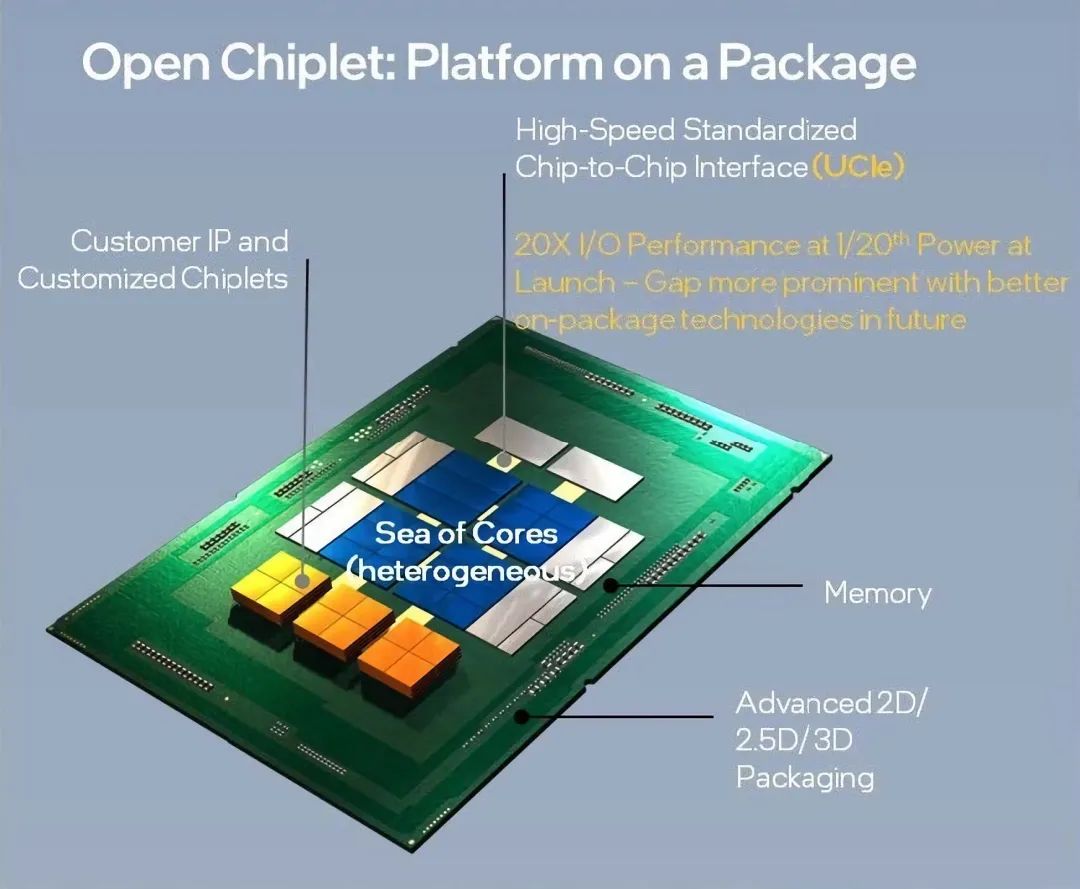

还有Chiplet技术,将原有的大芯片拆分成多颗体积更小、产量更高、不同功能的小芯片,经过再设计和再制造,最终通过系统级封装SiP异质整合成系统芯片,不仅不会增加原有芯片的面积,同时减少产品开发的时间成本及上市时程。

近日,日月光与AMD、Arm、Google Cloud、Intel、Meta、微软(Microsoft)、高通(Qualcomm)、三星(Samsung)和台积电(TSMC)等半导体业者共同组成UCIe (Universal Chiplet Interconnect Express) 产业联盟,推动芯片互连(die-to-die interconnect)技术标准化和促进开放式Chiplet生态系统。日月光在封装和互连平台技术的专业知识,有助于确保UCIe提出的标准切实可行,并且在封装制造具有商业可行性和成本效益。

UCIe在封装上实现开放式Chiplet生态系统 为确保封装顺利完成,不同的封装技术需要掌握好异质的机械性质,真正实现针对不同用途需求的系统级封装SiP集成,达到“芯片+封装+系统”的整合综效。日月光持续研发先进制程技术,洞悉市场趋势,协助客户减少芯片设计时程并加快产品开发速度。

审核编辑 :李倩

-

一文读懂系统级封装(SiP)技术:定义、应用与前景2024-12-31 8321

-

浅析先进封装的四大核心技术2023-09-28 5206

-

SiP与先进封装有什么区别2023-05-19 2985

-

先进封装四要素及发展趋势电子学习 2022-12-10

-

最新的系统级封装SiP发展趋势2022-11-24 2988

-

SIP封装和采用SiP工艺的DFN封装是什么2021-09-22 9235

-

SiP系统级封装对比先进封装HDAP二者有什么异同点?2021-03-15 9727

-

先进封装技术及发展趋势2020-10-12 19908

-

SiP与Chiplet成先进封装技术发展热点2020-09-17 10955

-

先进封装技术的发展趋势2018-11-23 3778

-

系统级封装(SiP)的发展前景(上)2018-08-23 4402

-

系统级封装(SiP)集成技术的发展与挑战2009-12-21 824

-

SoC与SiP混合设计出多样化手机2009-02-12 3489

全部0条评论

快来发表一下你的评论吧 !