HARSE工艺在先进封装技术的潜在应用

今日头条

描述

在本文中讲述了HARSE的工艺条件,其产生超过3微米/分钟的蚀刻速率和控制良好的、高度各向异性的蚀刻轮廓,还将成为展示先进封装技术的潜在应用示例。

在用作阳极硅衬底的 “光学工作台”示意图中显示,混合技术集成和封装使用第二光刻步骤,可以在硅中蚀刻出相对于激光器的精确深度和位置的沟槽,以便被动对准光纤,此外可以蚀刻晶片通孔,用作正面控制和/或驱动电路的光学或电学互连。

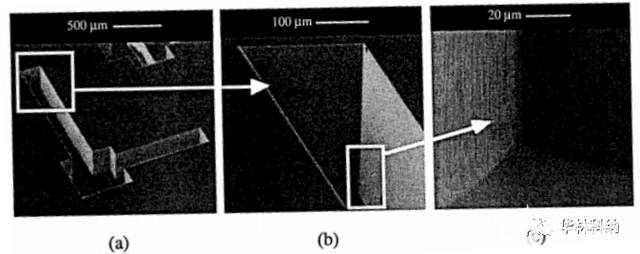

图1

图1展示了其中的几个概念,其中一张扫描电镜照片显示了同时蚀刻到约250微米深度的硅特征,在图1a中,中心正方形或器件定位器”可用于精确定位混合结构,而沟槽特征可用于电互连或延伸到光纤的晶片边缘,在图1b和1c中,高倍扫描电镜显微照片显示了侧壁和场的高各向异性和平滑蚀刻形态。

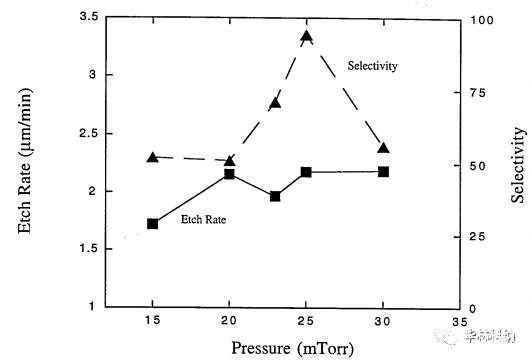

图2

为了实现被动自对准、蚀刻研究了作为室压、阴极射频功率和ICP源功率的函数的参数,在图2中,当阴极射频功率、等离子体源功率和气体流量保持不变时,硅蚀刻速率和硅对光刻胶的蚀刻选择性显示为压力的函数,通常导致离子能量和等离子体密度的变化,这强烈影响蚀刻性能,随着压力增加,表明在较低压力下反应物受限,这种相对于抗蚀剂的高蚀刻选择性使得能够以高纵横比进行深硅蚀刻(通常> 600 微米)。

蚀刻特性通常表现出对离子能量和等离子体的强烈依赖密度,离子能量影响蚀刻的物理成分,而等离子体密度可以影响工艺的物理和化学成分,当所有其它等离子体参数保持不变时,硅蚀刻速率和硅对光刻胶的蚀刻选择性被绘制为阴极射频功率的函数,随着射频功率的增加,硅蚀刻速率单调增加几乎3倍,由于阴极射频功率与直流偏压和离子轰击能量密切相关,较高离子能量下的较高蚀刻速率意味着蚀刻产物从表面的溅射解吸得到改善和/或硅表面分子的更有效的键断裂,随着离子轰击能量的增加,硅场区域中的聚合物的溅射效率也增加,该聚合物是在混合离子注入工艺的沉积周期中沉积的,在低离子能量条件下,聚合物可能不能有效地溅射,从而增加了混合蚀刻工艺的蚀刻开始时间并降低了硅蚀刻速率,尽管硅蚀刻速率更快,但由于聚合物和抗蚀剂的更有效溅射,随着射频功率的增加,蚀刻选择性显著降低。

尽管在高阴极rf功率等离子体下观察到更快的蚀刻速率条件下,蚀刻轮廓变得可重入,图中扫描电镜显微照片显示在(a) 8和(b) 25 W阴极射频功率下蚀刻的硅,在8W时,蚀刻剖面高度各向异性,蚀刻深度约为23微米,在25 W时,蚀刻深度约为30 微米,并且观察到显著的凹入轮廓。

在较高的射频功率下,凹入蚀刻轮廓可能是由于在较高的离子能量下溅射去除了侧壁聚合物蚀刻抑制剂,这导致了硅的横向蚀刻,对于高密度等离子体系统,离子能量和等离子体密度的影响更明显,因为与RIE相比,离子能量和等离子体密度可以更有效地解耦。随着等离子体源功率的增加,硅蚀刻速率增加了约30%,蚀刻选择性数据在约55∶1至90∶1的范围内不太稳定,在800瓦电感耦合等离子体源功率下观察到的低选择性还没有完全理解。

在HARSE工艺中观察到的高蚀刻选择性可归因于侧壁抑制剂聚合物的沉积,其也沉积在抗蚀剂上,尽管表面受到离子轰击,但沉积的聚合物增强了抗蚀剂的完整性,并显著降低了腐蚀速率。此外,HARSE工艺中较低的直流偏压显著降低了抗蚀剂侵蚀率,这 HARSE工艺产生约1.9 微米/分钟的蚀刻速率、高度各向异性的蚀刻轮廓和平滑的蚀刻形态,电感耦合等离子体中获得的通孔蚀刻轮廓很难控制,在通孔顶部具有凹入的侧壁轮廓和比通孔底部获得的开口宽得多的开口。

对于几种高电阻抗蚀剂工艺条件,显示了1至3.5微米/分钟的蚀刻速率,具有高度各向异性的轮廓和平滑的蚀刻形态,硅蚀刻速率和轮廓强烈依赖于阴极射频功率,随着离子能量的增加,蚀刻速率增加,蚀刻轮廓变得更加重要,凹入蚀刻轮廓可能是由于侧壁聚合物蚀刻抑制剂的溅射去除,硅蚀刻特性对室压和等离子体源功率的依赖性小得多,HARSE工艺在室温下操作,由于抗蚀剂的高蚀刻选择性,不需要硬光掩模。与电感耦合等离子体刻蚀相比,在较低的直流偏压下,该工艺产生了更多的各向异性刻蚀轮廓、更高的抗蚀选择性和更快的硅刻蚀速率,RSE工艺有望实现“混合技术”集成和封装。

审核编辑:汤梓红

-

先进封装技术的发展趋势2018-11-23 3769

-

宁波材料所在先进气体传感材料与传感器关键技术方面取得进展2019-01-21 1863

-

日本召开的VLSI 2019峰会上公开在先进制程工艺方面的进度2019-07-31 5249

-

中国在先进面板技术上对韩国企业发起挑战2020-04-03 2812

-

12种当今最主流的先进封装技术2021-04-01 38038

-

先进封装RDL-first工艺研究进展2023-12-07 4400

-

先进封装实现不同技术和组件的异构集成2023-12-14 2520

-

详细解读先进封装技术2024-01-23 5496

-

晶圆微凸点技术在先进封装中的应用2024-10-16 3556

-

混合键合在先进封装领域取得进展2024-11-27 1922

-

Chiplet在先进封装中的重要性2024-12-10 1539

-

CoWoS先进封装技术介绍2024-12-17 6106

-

先进封装中RDL工艺介绍2025-01-03 7084

-

先进封装工艺面临的挑战2025-04-09 1448

-

华宇电子分享在先进封装技术领域的最新成果2025-11-11 1493

全部0条评论

快来发表一下你的评论吧 !