如何从命令行获取和解析参数

描述

这是一篇技术干货快文,能够快速阅读完。文章内容是关于如何从命令行获取和解析参数,包括SystemVerilog本身支持的系统函数和UVM提供的函数封装,并给出示例代码和仿真结果。

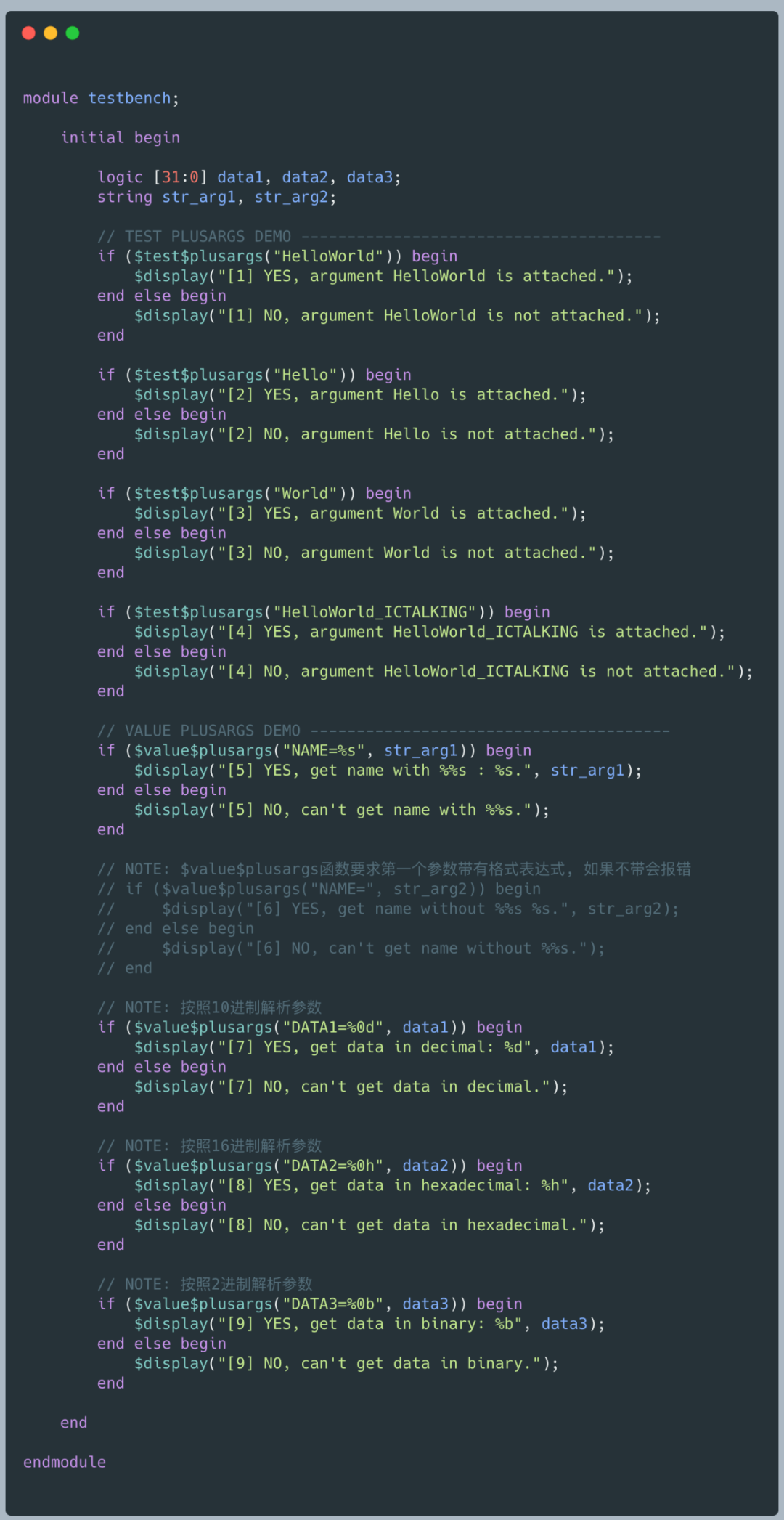

01 SV系统函数

通过命令行来传递参数在实际项目中算是常规操作,比如通过命令行参数来指定Testbench的配置信息等等。在SystemVerilog LRM规范里,命令行提供的仿真参数要求使用加号(+)作为引导,这部分参数可以被验证环境中的SV代码通过系统函数访问到。由于是额外增加的,这些参数也就被称之为plusargs。

访问plugargs的系统函数有$test$plusagrs(arg_string)和$value$plusargs(arg_string, target_var)。这两个系统函数都会根据用户指定的字符串arg_string,去检索plusargs列表。如果找到了,则系统函数返回值1;如果没有找到,返回值0。

其中$test$plusargs(arg_string)可以被用于判断命令行是否带了arg_string参数,以此来作为验证环境的配置开关;$value$plusargs(arg_string, target_var)则是在$test$plusargs的基础上,增加了对参数arg_string的值的解析:如果匹配到了arg_string,系统函数会将其值赋给target_var;如果没有找到,则不修改target_var的值。

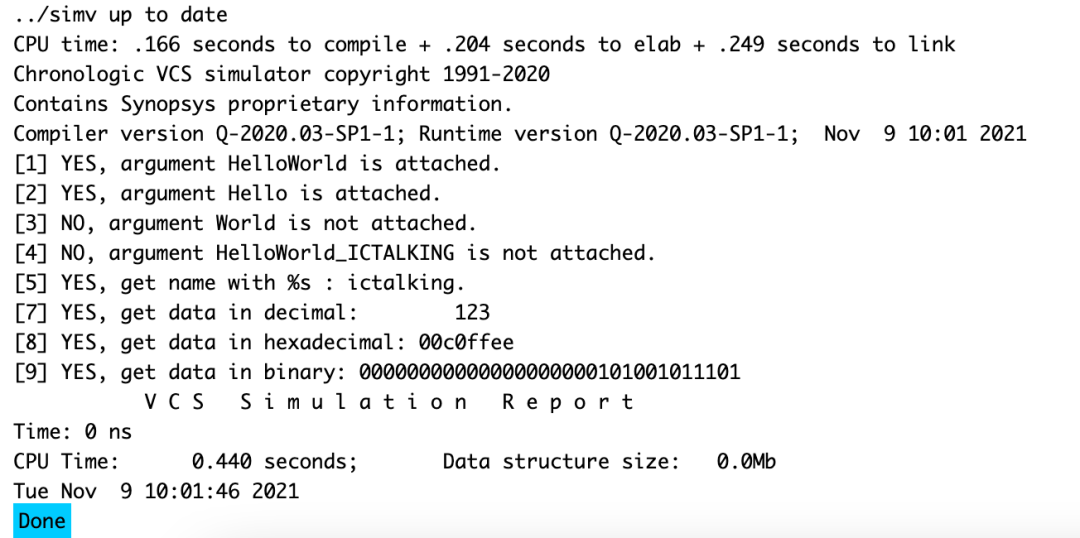

执行仿真命令:

./simv +vcs+lic+wait +HelloWorld +NAME=ictalking +DATA1=123 +DATA2=C0FFEE +DATA3=101001011101

仿真结果如下:

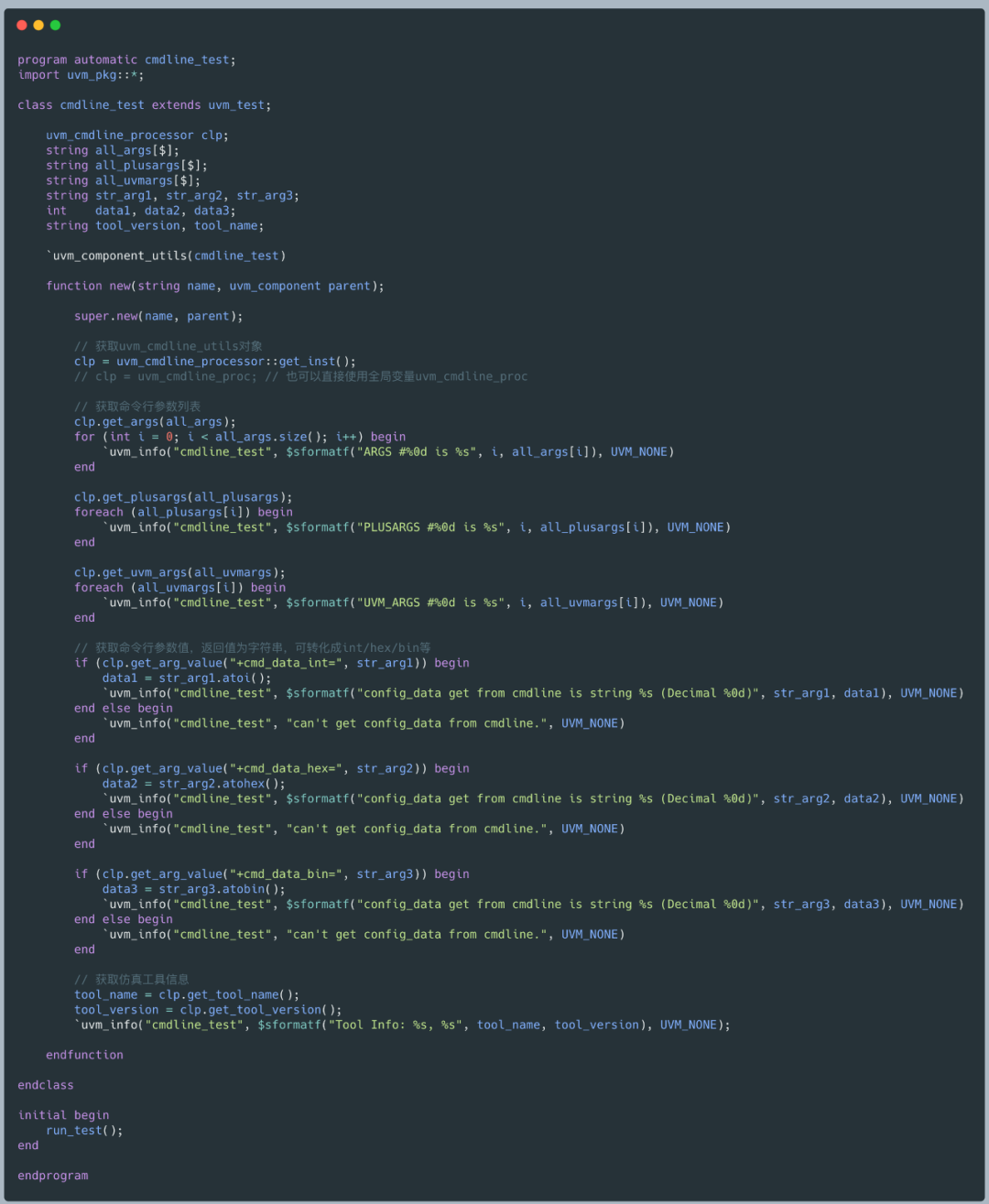

02 UVM_CMDLINE_PROCESSOR

UVM是个非常喜欢搞封装的类库。UVM中有个类叫uvm_cmdline_processor,该类继承自uvm_report_object,再往上就到uvm_object了。uvm_cmdline_processor提供的底层函数接口,说白了跟$test$plusargs和$value$plusargs没有什么大的区别,不过其中有匹配功能或返回参数列表的函数,对于uvm_root解析UVM配置相关的参数还是很有帮助的。

uvm_cmdline_processor全局单一例化,并提供了get_inst()静态方法用来获取对象句柄。UVM默认在初始化的时候,会构造uvm_cmdline_processor的全局对象,叫uvm_cmdline_proc。不过在实际使用中,我们还是可以按照习惯,先声明一个uvm_cmdline_processor句柄,然后通过get_inst()函数来指向uvm_cmdline_processor对象。

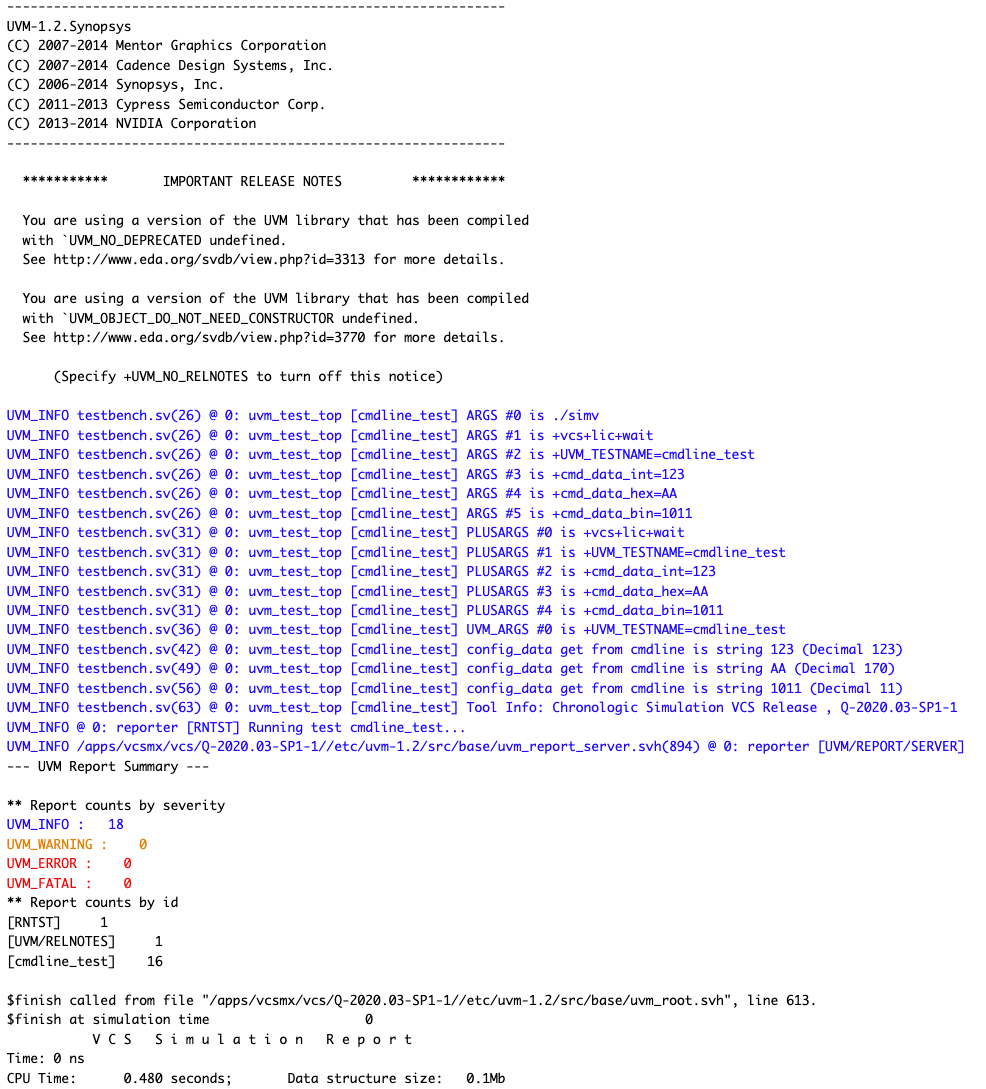

执行仿真命令:

./simv +vcs+lic+wait +UVM_TESTNAME=cmdline_test +cmd_data_int=123 +cmd_data_hex=AA +cmd_data_bin=1011

仿真结果如下:

原文标题:SystemVerilog | UVM | 获取命令行参数的方法,这些就够用了

文章出处:【微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

-

怎么从命令行执行Momentum2019-03-08 1680

-

如何从命令行指定程序员?2019-09-30 2136

-

如何从命令行注入宏?2019-10-31 1560

-

支持命令行传递的参数吗?2020-03-17 1433

-

Shell脚本命令行解析2020-04-03 1282

-

如何获取其它程序的命令行参数2010-10-14 352

-

C语言入门教程-命令行参数2009-07-29 2788

-

caxa命令行中的应用2009-10-18 2526

-

CMD的命令行高级教程2017-10-24 1297

-

自己动手实现命令行解析器2021-12-22 645

-

Shell命令行解释器简介2022-08-19 4048

-

Golang基于flag库实现一个命令行工具2022-10-28 1959

-

Fcoder从命令行批量转换为TIFF2023-05-22 1544

-

LabVIEW命令行调用exe传入的参数如何获取2023-10-11 4133

-

idea如何输入命令行参数2023-12-06 2020

全部0条评论

快来发表一下你的评论吧 !